Index 229

_10_V_AT_1_A

Published:2009/7/8 23:48:00 Author:May

Combination of LM195 power transistor IC and standard LM104 regulator gives negative output voltage with full overload protection and better than 2-mV load regula tion Input voltage must be only 2 V greater than output voltage,-″Linear Applications,Voi,2 National Semico"ductor、Santa Clara、CA'1976、AN-110,p4-5 (View)

View full Circuit Diagram | Comments | Reading(613)

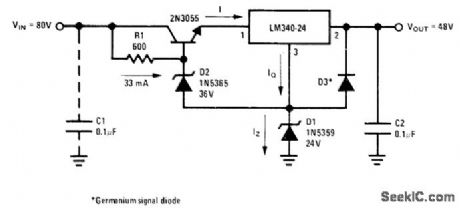

48_V_FROM_80_V

Published:2009/7/8 23:47:00 Author:May

Level-shifting transistorzener combination R1-D2 is used with zener D1 to keap voltage across LM340-24 regulator below maximum ratedvalue Addition of zenershas drawback of inoreasing output noise to about 2 mV P-P. Load regulation is 60 mV for pulsed load change from 5 mA to 1 A. Line reg-ulation is 0.01%/V of input voltage change for 500-mA load.- Linear Applications, Vol. 2, National Semiconductor, Santa Clara, CA, 1976, AN-103, p 10-11. (View)

View full Circuit Diagram | Comments | Reading(2012)

AUDIO_FREQUENCY_DOUBLER

Published:2009/7/8 23:44:00 Author:May

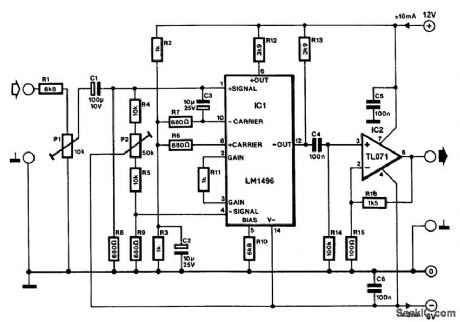

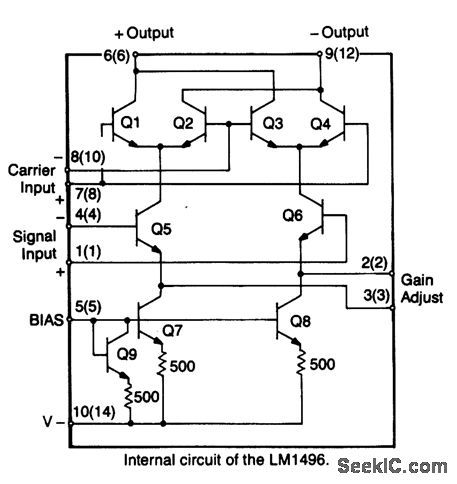

Often the frequency of a signal must be dou-bled: modulator/demodulator chip LM1496 is an ideal basis for this.

From trigonometry it is well known that:

2sitvrcosx= sin2x

and∶

sin2=1-xcos2x.

These equations indicate that the product of two pure sinusoidal signals of the same frequency is one signal of double that frequency. The purity of the original signals is important: composite signals would give rise to all sorts of undesired products.

The LM1496 can only process signals that are not greater than 25 mV: above that level, serious distortion will occur. The design is therefore pro-vided with a potential divider at its input. This addi-tion makes it possible, for instance, to arrange for a 500-mV input signal to result in a signal of only 25 mV at the input of the LM1496.

To provide a sufficiently high output signal, the output of IC1 is magnified by op amp IC2, which is connected as a noninverting amplifier. Because the output of IC1 contains a dc component of about 8 V, the coupling between the two stages must be via a capacitor, C4.

With values of R15 and R16 as shown, IC2 gives an amplification of 16 (24 dB). The overall amplifica-tion of the circuit depends on the level of the input signal: with an input of 1.2 V, the amplification is unity; when the input drops to 0.1 V, the amplification is just 0.1. The value of the input resistors has been fixed at 6800: this value gives a reasonable compromise between the requirements for a high input impedance and a low noise level.

To ensure good suppression of the input signal at the output, the voltages at pin 1 and pin 4 of IC1 must be absolutely identical to P4. It is possible, with the aid of a spectrum analyzer, to suppress the fundamental (input) frequency by 60 to 70 dB.

The output signal at pin 12 is distorted easily, because the IC is not really designed for this kind of operation. The distortion depends on the level of the input signal. At a frequency of 1 kHz and an input level of 100 mV, the distortion is about 0.6%; when the input level is raised to 500 mV, the distortion increases to 2.3%, and when the input level is 1 V, the distortion is 6%. The signal-to-noise ratio under these conditions varies between 60 and 80 dB.

The circuit draws a current of 10 mA from the positive supply line and 5 mA from the negative line.The phase shift between the input and output signals is about 45° (output lags). Finally, although the nor-mal output is taken from pin 12, a similar output that is shifted by 180° (with respect to that at pin 12), is available at pin 6. (View)

View full Circuit Diagram | Comments | Reading(1662)

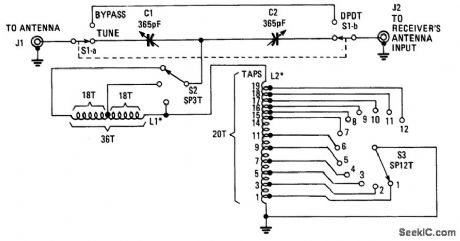

1_TO_30_MHz_ANTENNA_TUNER

Published:2009/7/8 23:39:00 Author:May

This tuner will match a random length wire antenna to a receiver or low-power transmitter (≤25 W) for optimum signal transfer. (View)

View full Circuit Diagram | Comments | Reading(2648)

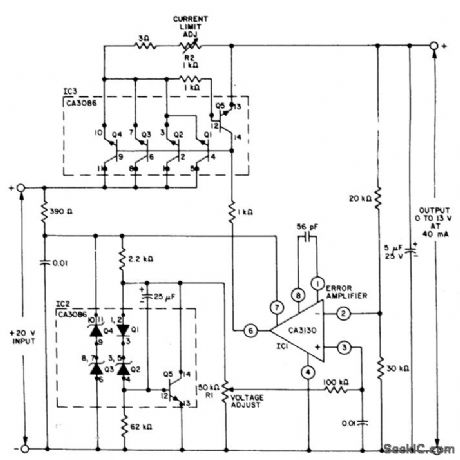

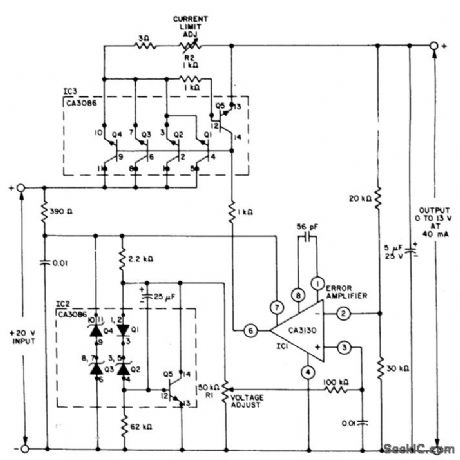

0_13_V_AT_40_mA

Published:2009/7/8 23:37:00 Author:May

Cornbination of RCA CA3130 opamp and two CA3086 NPN transistor arrays provides better than 0.01% regulation from no Ioad to full Ioad and input regulation of 0.02%/ V. Hum and noise output is less than 25 μV up to 100 kHz.- Linear Integrated Circuits and MOS/FET's, RCA Solid State Division, Somer-ville, NJ, 1977, p 236-243. (View)

View full Circuit Diagram | Comments | Reading(778)

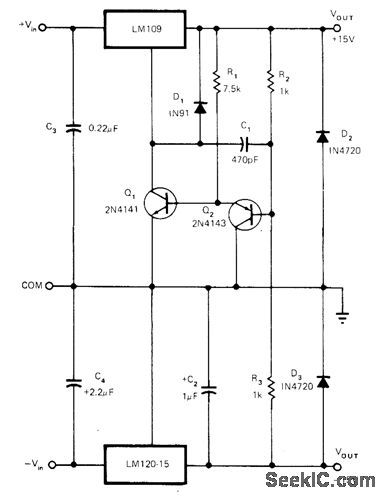

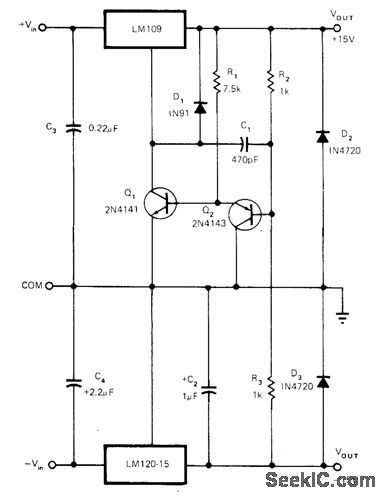

±15_V_WITH_TRACKING

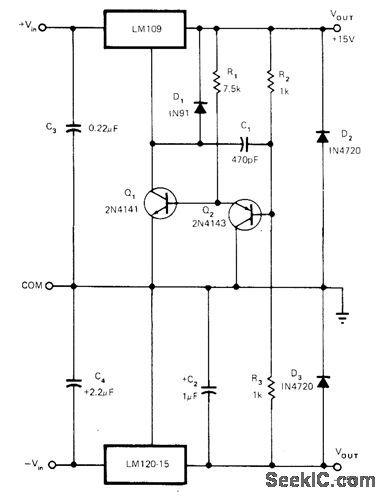

Published:2009/7/8 23:35:00 Author:May

In arrangement shown for National regulator ICs, positive output voltage tracks negative voltage to better than 1%. Ripple rejection is 80 dB for both outputs. Load regulation is 30 mV at 1 A for nega-tive outputand less than 10 mV for positive output. Circuit works well for output in range of 16 to ±15 V. C, provides stability.-C. T. Nel-son, Power Distribution and Regulation Can Be Simple, Cheap and Rugged, EDN Magazine, Feb. 20, 1973, p 52-58. (View)

View full Circuit Diagram | Comments | Reading(605)

LOW_COST_CRYSTAL_FILTERS

Published:2009/7/8 23:35:00 Author:May

Low-cost CB crystals can be used for these 9-MHz crystal ladder filters. Notice that the 27-MHz crystals (3rd overtone) are used on their fundamental frequencies. (View)

View full Circuit Diagram | Comments | Reading(2266)

PHOTOCELL_BRIDGE

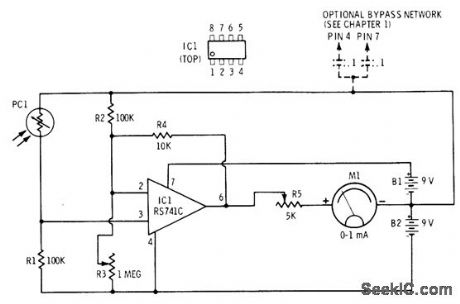

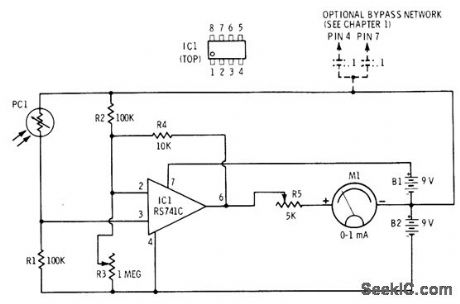

Published:2009/7/8 23:34:00 Author:May

Radio Shack 276-116 cadmium sulfide photocell is connected in Wheatstone bridge circuit. When bridge is bal-anced, RS741C opamp connected to opposite comers of bridge receives no voltage and meter reads zero. Light on photocell unbalances bridge and gives meter deflection. Can be used as high-sensitivity light meter. Adjust R3 until meter reads zero with photocell covered while R5 is at maximum resistance,adjust R5 until needle moves away from zero,rezero with R3,and repeat procedure until meter can no longerbe brought to zero,Sensitivityis now maximum,and uncovered photocell Will detectfiame from candle at 20 feet.-F.M.Mims,''Integrated Circuit Projects,vol 4,''Radio Shack,Fort Worth,TX,1977,2nd Ed.,p 29-35.

(View)

View full Circuit Diagram | Comments | Reading(1199)

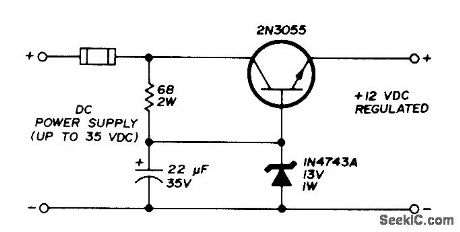

_12_V_AT_2_A

Published:2009/7/8 23:34:00 Author:May

Developed for unregulated 12-VDC supplies used by some amateurs with low-power VHF FM equipment, where no-load voltage may be 18 V or more. During transmit, voltage drops to about 12V, but on receive may exceed voltage ratings of small-signal transistors in transceiver. Use heatsinkwith transistor, and use 2-A fuse to protect transistor from shorted load.-J. Fisk, Circuits and Techniques, Ham Radio, June 1976, p 48-52. (View)

View full Circuit Diagram | Comments | Reading(518)

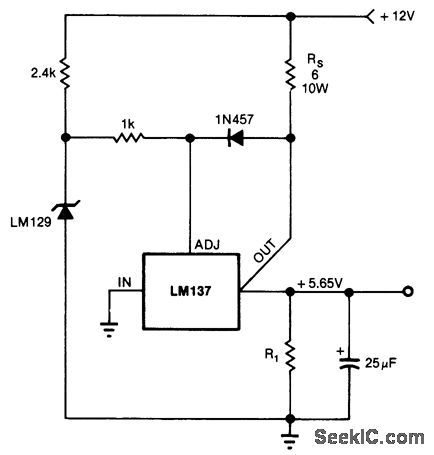

POSITIVE_SHUNT_REGULATION

Published:2009/7/8 23:34:00 Author:May

Connection shown for LM137 negative series regulator provides high-reliability positive shunt regulation for applications having high-voltage spike on raw DC supply. Output is 5.65 V.-P. Lefferts, Series Regulators Provide Shunt Regulation, EDNMagazine, Sept.5, 1978, p 158 and 160. (View)

View full Circuit Diagram | Comments | Reading(588)

20_kHz_ARC_WELDING_INVERTER

Published:2009/7/8 23:33:00 Author:May

The Class A series resonant inverter portrayed is well-known and respected for its high efftciency, low cost, and small size, provided that operating frequency is greater than about 3 kHz. The disadvantages are, at least in high power versions, the difftculty in effecting smooth RFI-free output voltage modulationwithout significant added complexity, and a natural tendency to run away under no-load (highQ) conditions.The 20-kHz control circuit (see Fig. 2) overcomes these shortcomings by feeding back into the asymmetrical thyristor trigger pulse generators (see Fig. 3) signals that simultaneously shut the inverter down, when its output voltage exceeds a preset threshold, then time-ratio modulates the output. This feedback is accomplished with full galvanic isolation between input and output thanks to an H11L opto-Schmitt coupler. The fundamental 20-kHz gate firing pulses are generated by a PUT relaxation oscillator Q1. The pulses are then amplified by transistors Q2 and Q3. The 20-kHz sinusoidal load current flowing in the pri-mary of the output transformer is then detected by current transformer CT1, with op amp A1 converting the sine wave into a square wave, whose transitions coincide with the load current zero points.Consequently, each time the output current changes, phase A1 also changes state and, via transistor Q4, either connects the thyristor gate to a -8 Vdc supply for minimum gate assisted turn-off time and highest reapplied dVldt capability or disables this supply to prepare the thyristor for subsequent firing.Modulation intelligence is coupled into this same H11L through two additional PUTs, Q6 and Q7, Q6 oscillates at a fixed 1.25 kHz, which establishes the modulation frequency. The duty cycle is determined by a second oscillator, Q7, whose conduction state, on or off, establishes or removes current from the H11L diode. With afundamental inverter frequency of 20 kHz and a modulation frequency of 1.25 kHz, the resultant time ratio-controlled power output is given by:where PM= 100% continuous output power. Minimum power is one cycle of 20 kHz (50 μs) in the 1.25-kHz modulation frame (800 μs), that is, 6.25% PM. (View)

View full Circuit Diagram | Comments | Reading(5204)

TUNABLE_BANDPASS_FILTER

Published:2009/7/8 23:33:00 Author:May

One of the difficulties in the design of higher-order tunable bandpass filters is achieving correct track-ing of the variable resistors in the RC networks. The use of switched capacitor networks can obviate that difficulty, as is shown in this filter.

The filter can be divided roughly into two stages: an oscillator that controls the electronic switches and the four phase-shift networks that provide the filtering proper. The oscillator, based on a 555, generates a pulsating signal whose frequency is adjustable over a wide range: the duty factor varies from 1:10 to 100:1.

Electronic switches ES1 through ES4 form the variable resistors whose value is dependent on the frequency of the digital signal. The operation of these switches is fairly simple. When they are closed, their resistance is about 60Ω; when they are open, it is virtually infinitely high. If a switch is closed for, say, 25% of the time, its average resistance is therefore 240Ω. Varying the open:closed ratio of each switch varies the equivalent average resistance. The switching rate of the switches must be much greater than the highest audio frequency to prevent audible interference between the audio and the clock signals.

The input signal causes a given direct voltage across C1, so the op amp can be operated in a quasisym-metric manner, in spite of the single supply voltage. The direct voltage is removed from the output signal by capacitor C10.

The fourth-order filter in the diagram can be used over the entire audio range and it has an ampliftca-tion of about 40, although this depends to some extent on the clock frequency. The bandwidth depends mainly on the set frequency. The circuit draws a current of not more than 15 mA. (View)

View full Circuit Diagram | Comments | Reading(4444)

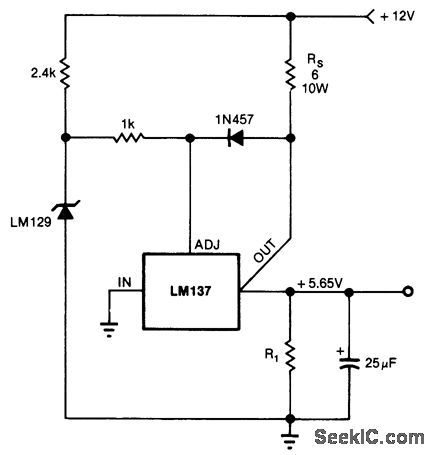

SUMMING_AMPLIFIER_CLAMPING_CIRCUIT

Published:2009/7/9 1:26:00 Author:May

This circuit is a traditional summing amplifier configuration with the addition of the dc clamping circuit The operation is quite simple; each component-synchro nization, color burst, picture information, etc.-of the composite video signal is applied to its own input terminal of the amplifter. These signals combine algebraically and form the composite signal at the output. The clamping circuit, if used, restores the 0-V reference of the composite signal. (View)

View full Circuit Diagram | Comments | Reading(973)

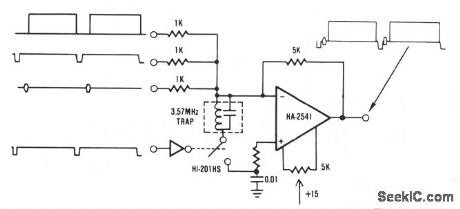

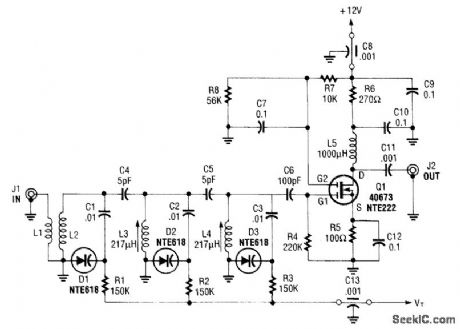

DUAL_GATE_MOSFET_RF_AMP_STAGE

Published:2009/7/9 1:25:00 Author:May

The use of a double-tuned input and a single-tuned output yield superior RF selectivity to that of equivalent single-tuned designs. AGC, if required, can be added to gate 2 of Q1, and should drive gate 2 negative for decreased gain. (View)

View full Circuit Diagram | Comments | Reading(1670)

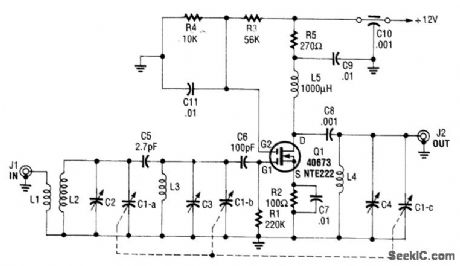

VARACTOR_TUNED_PRESELECTOR

Published:2009/7/9 1:20:00 Author:May

Varactor diodes replace the conventional 365-pF tuning capacitors, which reduces size and weight when used as a turned RF stage for AM broadcast applications. Selectivity is good enough for use as a TRF receiver if a detector is connected to J2. (View)

View full Circuit Diagram | Comments | Reading(1072)

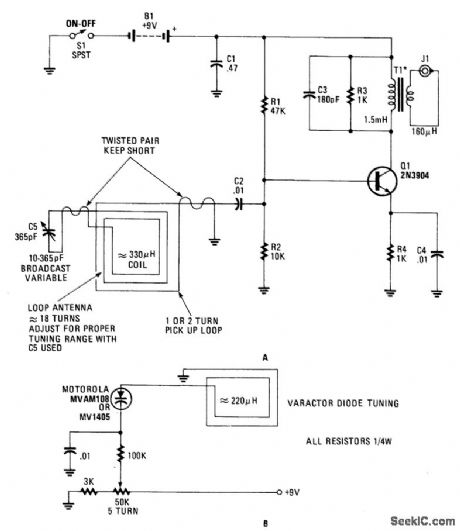

BROADCAST_BAND_BOOSTER

Published:2009/7/9 1:19:00 Author:May

The use of a loop antenna oflarge size (12×18″)provides a large signal pickup at AM broadcast frequencles.It has about 18 turns. T1 is a toroidal transformer of about⒊1 turns ratio (not critical).Theprimary winding should have about 1.5 mH inductance. By using the circuit at (B),a varactor diode can beused In place of the 10- to 365-pF variable capacitor. (View)

View full Circuit Diagram | Comments | Reading(889)

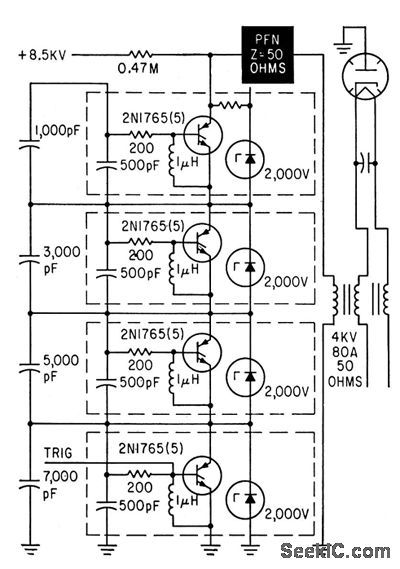

300_KW_MAGNETRON_MODULATOR

Published:2009/7/20 23:55:00 Author:Jessie

Trigger is applied to first of four 2-kv switch modules arranged in series, for simultaneous triggering of other modules to furnish 16-kv 20-amp pulse to type 7208 Ku-band coaxial magnetron through standard 50-ohm pulseforming network PFN.-F. A. Gateka and M. L.Embree, Semiconductor Modulators for Modern Magnetrons, Electronics, 35:37, p 42-45. (View)

View full Circuit Diagram | Comments | Reading(1233)

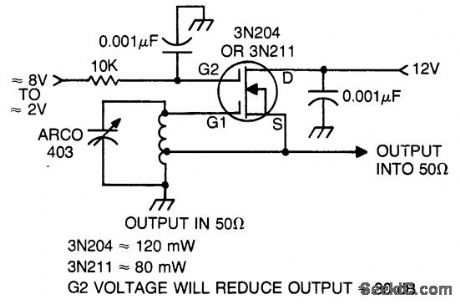

145_MHz_RF_oscillator_using_a_3N204_3N211_dual_gate_MOSFET

Published:2009/7/20 23:56:00 Author:Jessie

145 MHz RF oscillator using a 3N204/3N211 dual-gate MOSFET (courtesy Texas Instruments Incorporated). (View)

View full Circuit Diagram | Comments | Reading(2513)

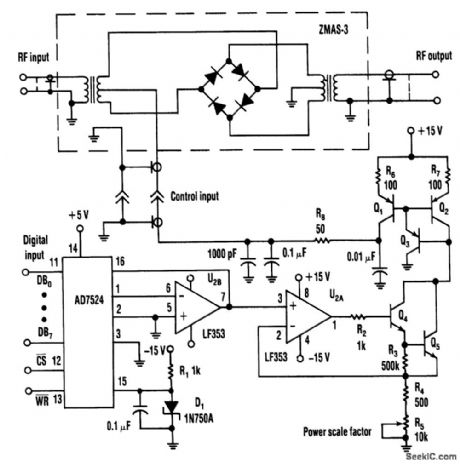

RF_ATTENUATOR

Published:2009/7/8 23:29:00 Author:May

A balanced mixer is used as a control element in this circuit. An Analog Devices AD7524 D/A con-verter drives a voltage-controlled current source using two LF353s and several transistors to control the balanced mixer, a Mini Circuits Lab Z MAS-3

(View)

View full Circuit Diagram | Comments | Reading(1362)

ULTRASONIC_PEST_REPELLER

Published:2009/7/8 23:28:00 Author:May

This circuit is a 555 timer IC connected as a square-wave generator. Its base frequency is approximately 45 kHz, as determined by the values of R1, R2, and C1. The 45-kHz carrier is frequency modulated by a modified trapizoidal voltage waveform applied to pin 5 of the 555 timer. That modulating voltage is developed by a network consisting of C2, R3, and R4 connected across one leg of the bridge rectifier. The sweep is approximately 20 kHz on each side of the base frequency. The speaker is a 2-inch piezoelectric tweeter. (View)

View full Circuit Diagram | Comments | Reading(0)

| Pages:229/471 At 20221222223224225226227228229230231232233234235236237238239240Under 20 |

Circuit Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit