WT7010-S080WT-1B, WT74, WT7510 Selling Leads, Datasheet

MFG:N/A Package Cooled:NA/ D/C:0311+

WT7010-S080WT-1B, WT74, WT7510 Datasheet download

Part Number: WT7010-S080WT-1B

MFG: N/A

Package Cooled: NA/

D/C: 0311+

MFG:N/A Package Cooled:NA/ D/C:0311+

WT7010-S080WT-1B, WT74, WT7510 Datasheet download

MFG: N/A

Package Cooled: NA/

D/C: 0311+

Want to post a buying lead? If you are not a member yet, please select the specific/related part number first and then fill the quantity and your contact details in the "Request for Quotation Form" on the left, and then click "Send RFQ".Your buying lead can then be posted, and the reliable suppliers will quote via our online message system or other channels soon.

TOP

PDF/DataSheet Download

Datasheet: WT7012

File Size: 71589 KB

Manufacturer: ETC [ETC]

Download : Click here to Download

PDF/DataSheet Download

Datasheet: WT7012

File Size: 71589 KB

Manufacturer: ETC [ETC]

Download : Click here to Download

PDF/DataSheet Download

Datasheet: WT7510

File Size: 82554 KB

Manufacturer: ETC [ETC]

Download : Click here to Download

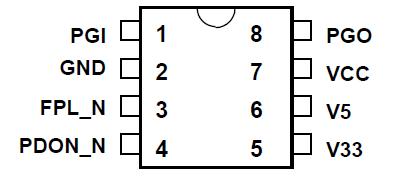

The WT7510 provides protection circuits, power good output (PGO), fault protection latch (FPL_N),and a protection detector function (PDON_N) control. It can minimize external components of switching power supply systems in personal computer.

The Over Voltage Detector (OVD) monitors 3.3V, 5V, 12V input voltage level. The Under Voltage Detector (UVD) monitors 3.3V, 5V input voltage level. When OVD or UVD detect the fault voltage level,the FPL_N is latched HIGH and PGO go low. The latch can be reset by PDON_N goo HIGH. There is 2.4 ms delay time for PDON_N turn off FPL_N.

When OVD and UVD detect the right voltage level, the power good output (PGO) will be issue.

• The Over Voltage Detector (OVD) monitors 3.3V, 5V, 12V input voltage level.

• The Under Voltage Detector (UVD) monitors 3.3V, 5V input voltage level.

• Both of the power good output (PGO) and fault protection latch (FPL_N) are Open Drain Output.

• 75 ms time delay for UVD.

• 300 ms time delay for PGO.

• 38 ms for PDON_N input signal Debounce.

• 73 us for internal signal Deglitches.

• 2.4 ms time delay for PDON_N turn-off FPL_N.