STA013T013TR, STA013TR, STA015 Selling Leads, Datasheet

MFG:ST Package Cooled:QFP44 D/C:99/00+

STA013T013TR, STA013TR, STA015 Datasheet download

Part Number: STA013T013TR

MFG: ST

Package Cooled: QFP44

D/C: 99/00+

MFG:ST Package Cooled:QFP44 D/C:99/00+

STA013T013TR, STA013TR, STA015 Datasheet download

MFG: ST

Package Cooled: QFP44

D/C: 99/00+

Want to post a buying lead? If you are not a member yet, please select the specific/related part number first and then fill the quantity and your contact details in the "Request for Quotation Form" on the left, and then click "Send RFQ".Your buying lead can then be posted, and the reliable suppliers will quote via our online message system or other channels soon.

TOP

PDF/DataSheet Download

Datasheet: STA001

File Size: 237395 KB

Manufacturer: STMICROELECTRONICS [STMicroelectronics]

Download : Click here to Download

PDF/DataSheet Download

Datasheet: STA001

File Size: 237395 KB

Manufacturer: STMICROELECTRONICS [STMicroelectronics]

Download : Click here to Download

PDF/DataSheet Download

Datasheet: STA015

File Size: 251913 KB

Manufacturer: STMICROELECTRONICS [STMicroelectronics]

Download : Click here to Download

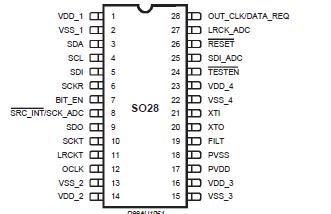

The STA015 is a fully integrated high flexibility MPEG Layer III Audio Decoder, capable of decoding Layer III compressed elementary streams, as specified in MPEG 1 and MPEG 2 ISO standards. The device decodes also elementarystreams compressed by using low sampling rates, as specified byMPEG 2.5.

STA015 receives the input data through a Serial Input Interface. The decoded signal is a stereo, mono, or dual channel digital output that can be sent directly to a D/A converter, by the PCM Output Interface. This interface is software programmable to adapt the STA015 digital output to the most common DACs architectures used on the market.

The functional STA015 chip partitioning is described in Fig.1 and Fig.2.

| Symbol | Parameter |

Value |

Unit |

| VDD | Power Supply |

-0.3 to 4 |

V |

| Vi | Voltage on input pins |

-0.3 to VDD+0.3 |

V |

| VO | Voltage on output pins |

-0.3 to VDD+0.3 |

V |

| Tstg | Storage Temperature |

-40 to 150 |

|

| Toper | Operative ambient temp |

-25 to 85 |

· SINGLE CHIP MPEG2 LAYER 3 DECODER SUPPORTING:

- All features specified for Layer III in ISO/IEC 11172-3 (MPEG 1 Audio)

- All features specified for Layer III in ISO/IEC 13818-3.2(MPEG 2 Audio)

- Lower sampling frequenciessyntax extension,(not specified by ISO) called MPEG 2.5

· DECODES LAYER III STEREO CHANNELS,DUAL CHANNEL, SINGLE CHANNEL (MONO)

· SUPPORTING ALL THE MPEG 1 & 2 SAMPLING FREQUENCIES AND THE EXTENSION TO MPEG 2.5: 48, 44.1, 32, 24, 22.05, 16, 12, 11. 025, 8 KHz

· ACCEPTS MPEG 2.5 LAYER III ELEMENTARY COMPRESSED BITSTREAM WITH DATA RATE FROM 8 Kbit/s UP TO 320 Kbit/s

· ADPCM CODEC CAPABILITIES:

- sample frequencyfrom 8 kHz to 32 kHz

- sample size from8 bits to 32 bits

- encodingalgorithm:DVI,ITU-G726pack (G723-24,G721,G723-40)

- Tone controlandfast-forwardcapability

· EASY PROGRAMMABLE GPSO INTERFACE FOR ENCODED DATA UP TO 5Mbit/s (TQFP44 & LFBGA 64)

· DIGITALVOLUME

· BASS & TREBLECONTROL

· SERIAL BITSTREAM INPUT INTERFACE

· EASY PROGRAMMABLE ADC INPUT INTERFACE

· ANCILLARY DATA EXTRACTION VIA I2C INTERFACE.

· SERIAL PCM OUTPUT INTERFACE (I2S AND OTHER FORMATS)

· PLL FOR INTERNAL CLOCK AND FOR OUTPUT PCM CLOCK GENERATION

· CRC CHECK AND SYNCHRONISATION ERROR DETECTION WITH SOFTWARE INDICATORS

· I2C CONTROL BUS

· LOW POWER 2.4V CMOS TECHNOLOGY

· WIDE RANGE OF EXTERNAL CRYSTALS FREQUENCIES SUPPORTED