Features: • Synchronizes to clock-and-sync-pair to maintain minimal phase skew between the master-clock and the redundant slave-clock

• Supports ITU-T G.813 option 1, G.823 for 2048 kbs and G.824 for 1544 kbs interfaces

• Supports Telcordia GR-1244-CORE Stratum 3/4/4E

• Supports ANSI T1.403 and ETSI ETS 300 011 for ISDN primary rate interfaces

• Accepts three input references and synchronizes to any combination of 2 kHz, 8 kHz, 1.544 MHz, 2.048 MHz, 8.192 MHz, 16.384 MHz or 19.44 MHz inputs

• Provides a range of clock outputs: 1.544 MHz (DS1), 2.048 MHz (E1), 3.088 MHz, 16.384 MHz, and 19.44 MHz (SDH), and either 4.096 MHz and 8.192 MHz or 32.768 MHz and 65.536 MHz, and a choice of 6.312 MHz (DS2), 8.448 MHz (E2), 44.736 MHz (DS3) or 34.368 MHz (E3)

• Provides 5 styles of 8 kHz framing pulses and a 2 kHz multi-frame pulse

• Holdover frequency accuracy of 1x10-8

• Selectable loop filter 1.8 Hz, 3.6 Hz or 922 Hz

• Less than 20 psrms intrinsic jitter on the 19.44 MHz output clock, compliant with GR-253-CORE OC-3 and G.813 STM-1 specifications

• Less than 0.6 nspp intrinsic jitter on all output clocks and frame pulses

• Manual or Automatic hitless reference switching

• Provides Lock, Holdover and selectable Out of Range indication

• Simple hardware control interface

• Selectable external master clock source: Clock Oscillator or Crystal

Application• Synchronization and timing control for multi-trunk SDH and T1/E1 systems such as DSLAMs, Gateways and PBXs

• Clock and frame pulse source for AdvancedTCA™- and other time division multiplex (TDM) buses

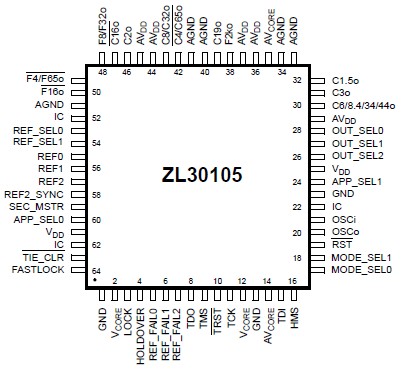

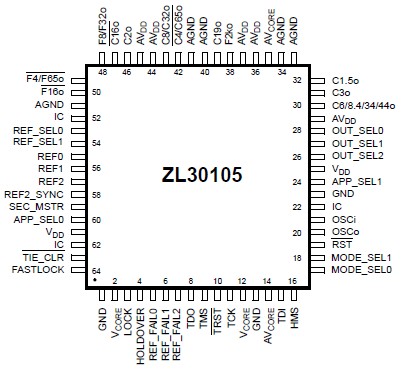

Pinout Specifications

Specifications

| |

Parameter |

Symbol |

Min. |

Max. |

UNIT |

| 1 |

Supply voltage |

V DD_R |

-0.5 |

4.6 |

V |

| 2 |

Core supply voltage |

V CORE_R |

-0.5 |

2.5 |

V |

| 3 |

Voltage on any digital pin |

VPIN |

-0.5 |

6 |

V |

| 4 |

Voltage on OSCi and OSCo pin |

VOSC |

-0.3 |

VDD + 0.3 |

V |

| 5 |

Current on any pin |

IPIN |

|

30 |

mA |

| 6 |

Storage temperature |

TST |

-55 |

125 |

|

| 7 |

TQFP 64 pin package power dissipation |

PPD |

|

|

mW |

| 8 |

ESD rating |

VESD |

|

2 |

kV |

* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

* Voltages are with respect to ground (GND) unless otherwise stated.DescriptionThe ZL30105 SDH/PDH System Synchronizer contains a digital phase-locked loop (DPLL), which provides timing and synchronization for SDH and T1/E1 transmission equipment. It provides advanced support for systems deploying redundant clocks.

The ZL30105 generates SBI, ST-BUS and other TDM clock and framing signals that are phase locked to one of three network references or to a system master-clock reference. It helps ensure system reliability by monitoring its references for frequency accuracy and stability and by maintaining tight phase alignment between the master-clock and slave-clock outputs even in the presence of high network jitter.

The ZL30105 is intended to be the central timing and synchronization resource for network equipment that complies with ITU-T, Telcordia, ETSI and ANSI network specifications.

ZL30105 Data Sheet

ZL30105 Data Sheet