Features: • 3.3-V core logic with universal PCI interfaces compatible with 3.3-V and 5-V PCI signaling environments

• Supports serial bus data rates of 100, 200, and 400 Mbits/s

• Provides bus-holding buffers on physical interface for low-cost single-capacitor isolation

• Supports physical write posting of up to three outstanding transactions

• Serial ROM interface supports 2-wire devices

• Supports external cycle timer control for customized synchronization

• Implements PCI burst transfers and deep FIFOs to tolerate large host latency

• Provides two general-purpose I/Os

• Fabricated in advanced low-power CMOS process

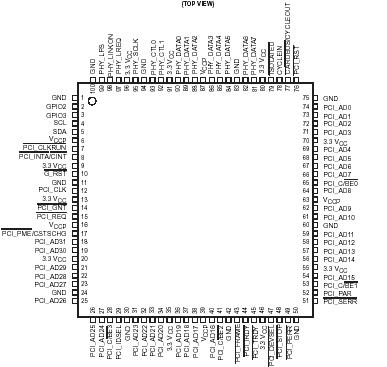

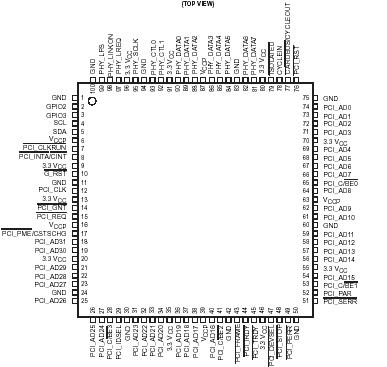

• Packaged in 100-terminal PQFP (PZ)

• Supports PCI_CLKRUN protocol

• Drop-in replacement for the TSB12LV22 device

• Supports PCI and CardBus applications

• Digital video and audio performance enhancementsPinout SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0.5 V to 3.6 V

SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0.5 V to 3.6 V

Supply voltage range, VCCP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0.5 V to 5.5 V

Input voltage range for PCI, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . .0.5 to VCCP + 0.5 V

Input voltage range for Miscellaneous and PHY interface, VI . . . . . . . . . . . . .0.5 to VCCI + 0.5 V

Output voltage range for PCI, VO V . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . .0.5 to VCCP + 0.5

Input voltage range for Miscellaneous and PHY interface, VO . . . . . . . . . . . . . .0.5 to VCCP + 0.5 V

Input clamp current, IIK (VI < 0 or VI > VCC) (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . .±20 mA

Output clamp current, IOK (VO < 0 or VO > VCC) (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . .±20 mA

NOTES: 1. Applies to external input and bidirectional buffers. For 5-V tolerant use VI > VCC. For PCI use VI > VCCP.

2. Applies to external output and bidirectional buffers. For 5-V tolerant use VO > VCC. For PCI use VO > VCCP.

Storage temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65°C to 150°CDescriptionThe Texas Instruments TSB12LV23A device, the OHCI-Lynx� PCI-based IEEE 1394 host controller, is a PCI-to-1394 host controller compatible with the latest PCI Local Bus, PCI Bus Power Management Interface, IEEE 1394-1995, and 1394 Open Host Controller Interface Specifications. The chip provides the IEEE 1394 link function

and is compatible with serial bus data rates of 100 Mbits/s, 200 Mbits/s, and 400 Mbits/s.

As required by the 1394 Open Host Controller Interface Specification (OHCI) and the IEEE 1394a-2000 specification, internal control registers are memory-mapped and nonprefetchable. The PCI configuration header is accessed through configuration cycles specified by PCI, and provides plug-and-play (PnP) compatibility. Furthermore, the TSB12LV23A device is compliant with the PCI Bus Power Management Interface Specification, according to the PC 99 Design Guide requirements. The TSB12LV23A device supports the D0, D2, and D3 power states.

The TSB12LV23A design provides PCI bus master bursting, and is capable of transferring a cacheline of data at 132 Mbytes/s after connection to the memory controller. Because PCI latency can be large, deep FIFOs are provided to buffer 1394 data.

The TSB12LV23A device provides physical write posting buffers and a highly tuned physical data path for SBP-2 performance. The TSB12LV23A device also provides multiple isochronous contexts, multiple cacheline burst transfers, advanced internal arbitration, and bus-holding buffers on the PHY/link interface.

The TSB12LV23A device implements an enhancement for formatted DV and audio/music isochronous transmissions which implement the common isochronous packet (CIP) format defined by IEC61883. The enhancements to the isochronous DMA contexts are implemented as hardware support for the synchronization time stamp for both DV and audio/music CIP formats. The TSB12LV23A device supports modification of the synchronization time stamp field to ensure that the value inserted via software is not stale, that is, less than the current cycle timer, when the packet is transmitted.

An advanced CMOS process is used to achieve low power consumption with operation at PCI clock rates up to 33 MHz.

SLLS411 Data Sheet

SLLS411 Data Sheet