Features: • Fully supports provisions of IEEE 1394-1995 standard for high-performance serial bus† and the IEEE 1394a-2000 supplement

• Fully interoperable with FireWireE and i.LINKE implementation of IEEE Std 1394

• Meets IntelE Mobile Power Guideline 2000

• Full IEEE 1394a-2000 support includes: connection debounce, arbitrated short reset, multispeed concatenation, arbitration acceleration, fly-by concatenation, and port disable/suspend/resume

• Power-down features to conserve energy in battery-powered applications include: automatic device power down during suspend, PCI power management for link-layer, and inactive ports powered down

• Ultra-low-power sleep mode

• Provides two IEEE 1394a-2000 fully compliant cable ports at 100/200/400 megabits per second (Mbits/s)

• Cable ports monitor line conditions for active connection to remote node

• Cable power presence monitoring

• Separate cable bias (TPBIAS) for each port

• 3.3-V core logic with universal PCI interfaces compatible with 3.3-V and 5-V PCI signaling environments

• Physical write posting of up to three outstanding transactions

• Implements PCI burst transfers and deep FIFOs to tolerate large host latency

• Supports PCI-CLKRUN protocol

• External cycle timer control for customized synchronization

• Extended resume signaling for compatibility with legacy DV components

• PHY-Link logic performs system initialization and arbitration functions

• PHY-Link encode and decode functions included for data-strobe bit level encoding

• PHY-Link incoming data resynchronized to local clock

• Low-cost 24.576-MHz crystal provides transmit and receive data at 100, 200, and 400 Mbits/s

• Node power class information signaling for system power management

• Serial ROM interface supports 2-wire devices

• Provides two general-purpose I/Os

• Register bits give software control of contender bit, power class bits, link active control bit, and IEEE 1394a-2000 features

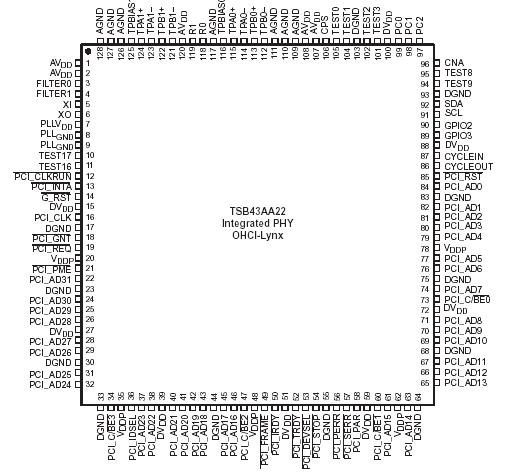

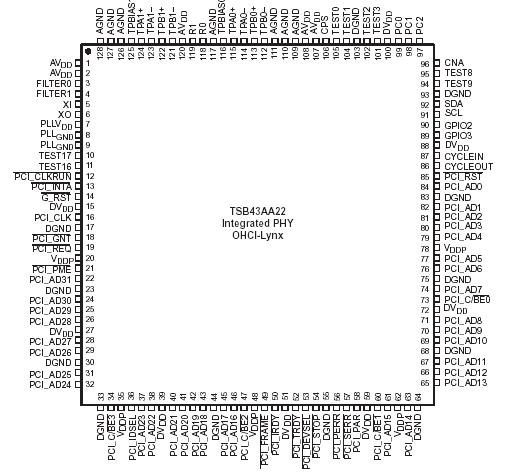

• Fabricated in advanced low-power CMOS processPinout SpecificationsSupply voltage range: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .AVDD 0.5 V to 3.6 V

SpecificationsSupply voltage range: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .AVDD 0.5 V to 3.6 V

DVDD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0.5 V to 3.6 V

PLLVDD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0.5 V to 3.6 V

VDDP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0.5 V to 5.5 V

Input voltage range for PCI, VI, PHY, and Miscellaneous . . . . .. . . . .0.5 to DVDD + 0.5 V

Output voltage range for PCI, VO, PHY, and Miscellaneous . . . . . . .0.5 to DVDD + 0.5 V

Input clamp current, IIK (VI < 0 or VI > VDD) (see Note 1) . . . . . . . . . . . . . . . . . .±20 mA

Output clamp current, IOK (VO < 0 or VO > VDD) (see Note 2) . . . . . . . . . . . . . . ±20 mA

Storage temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . 65°C to 150°C

Electrostatic discharge (see Note 3) . . . . . . . . . . . . . . . . . . . . . . . . . . .HBM:2 kV, MM:200 V

Continuous total power dissipation . . . . . . . . . . . . . . . . . . . .See Dissipation Rating Table

Operating free-air temperature, TA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to 70°C

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65°C to 150°C

NOTES: 1. Applies to external input and bidirectional buffers. For 5-V tolerant use VI > VDDI. For PCI use VI > VDDP.

2. Applies to external output and bidirectional buffers. For 5-V tolerant use VO > VDDI. For PCI use VO > VDDP.

3. HBM is human body model, MM is machine model.DescriptionThe Texas Instruments TSB43AA22 device is an integrated 1394a-2000 OHCI PHY/link layer controller device that is fully compliant with the PCI Local Bus Specification, the PCI Bus Power Management Interface Specification, the IEEE 1394-1995 standard, the IEEE 1394a-2000 supplement, and the 1394 Open Host Controller Interface

Specification. It is capable of transferring data between the 33-MHz PCI bus and 1394 bus at 100 Mbits/s, 200 Mbits/s, and 400 Mbits/s. The TSB43AA22 device provides two 1394 ports which have separate cable bias (TPBIAS). The TSB43AA22 device also supports IEEE 1394a-2000 power-down features for battery-operated applications and arbitration enhancements.

As required by the 1394 Open Host Controller Interface Specification (OHCI) and the IEEE 1394a-2000 specification, internal control registers are memory-mapped and nonprefetchable. The PCI configuration header is accessed through configuration cycles specified by PCI, and provides plug-and-play (PnP) compatibility. Furthermore, the TSB43AA22 device is compliant with the PCI Bus Power Management Interface Specification as specified by the PC 99 Design Guide requirements. The TSB43AA22 device supports the D0, D2, and D3 power states.

The TSB43AA22 design provides PCI bus master bursting, and it is capable of transferring a cacheline of data at 132 Mbytes/s after connection to the memory controller. Because PCI latency can be large, deep FIFOs are provided to buffer the 1394 data.

The TSB43AA22 device provides physical write posting buffers and a highly tuned physical data path for SBP-2 performance. The TSB43AA22 device also provides multiple isochronous contexts, multiple cacheline burst transfers, advanced internal arbitration, and bus holding buffers.

An advanced CMOS process is used to achieve low power consumption that allows the TSB43AA22 device to operate at PCI clock rates up to 33 MHz.

The TSB43AA22 device provides the digital and analog transceiver functions needed to implement a two-port node in a cable-based IEEE 1394 network. Each cable port incorporates two differential line transceivers. The transceivers include circuitry to monitor the line conditions as needed for determining connection status, for initialization and arbitration, and for packet reception and transmission.

The TSB43AA22 device requires only an external 24.576-MHz crystal as a reference for the cable ports. An external clock may be provided instead of a crystal. An internal oscillator drives an internal phase-locked loop (PLL), which generates the required 393.216-MHz reference signal. This reference signal is internally divided to provide the clock signals used to control transmission of the outbound encoded strobe and data information. A 49.152-MHz clock signal is supplied to the integrated LLC for synchronization and is used for resynchronization of the received data.

Data bits to be transmitted through the cable ports are received from the integrated LLC and are latched internally in synchronization with the 49.152-MHz system clock. These bits are combined serially, encoded, and transmitted at 98.304, 196.608, or 393.216 Mbits/s (referred to as S100, S200, and S400 speeds, respectively) as the outbound data-strobe information stream. During transmission, the encoded data information is transmitted differentially on the TPB cable pair(s), and the encoded strobe information is transmitted differentially on the TPA cable pair(s).

During packet reception, the TPA and TPB transmitters of the receiving cable port are disabled, and the receivers for that port are enabled. The encoded data information is received on the TPA cable pair, and the encoded strobe information is received on the TPB cable pair. The received data-strobe information is decoded to recover the receive clock signal and the serial data bits. The serial data bits are resynchronized to the local 49.152-MHz system clock and sent to the integrated LLC. The received data is also transmitted (repeated) on the other active (connected) cable ports.

SLLS358A Data Sheet

SLLS358A Data Sheet