Features: Low propagation delays - 2ns maximum for 3.3V,2.5ns maximum for 2.7V

Fast output enable/disable times of 5ns maximum

FastBus Charge current to minimize the bus settlingtime during active capacitive loading

2.7 to 3.6V VCC supply operation;LV-TTL compatible input and output levels with 3-statecapability

Industry standard pinout compatible to FCT, ALV, LCX,LVT, and other low voltage logic families

ESD protection exceeds 2000V

Full output swing for increased noise margin

Undershoot and overshoot protection to 400mVtypically

Low ground bounce design

Pinout SpecificationsVCC ............................................................................. 7V

SpecificationsVCC ............................................................................. 7V

DC Input Voltage ............................ 0.3V to VCC + 0.3V

AC Input Voltage (PW < 20ns) .............................. 3.0V

DC Output Voltage ................................... 0.3V to 7VDC

Storage Temperature Range .................... 65 to 150

Junction Temperature .............................................. 150

Lead Temperature (Soldering, 10sec) ...................... 150

Thermal Impedance (qJA) ..................................... 76/WDescriptionThe ML65F16244 is a BiCMOS, 16-bit buffer/line driverwith 3-state outputs. This device was specifically designedfor high speed bus applications. Its 16 channels supportpropagation delay of 2ns maximum, and fast outputenable and disable times of 5ns or less to minimizedatapath delay.

This ML65F16244 is designed to minimize undershoot,overshoot, and ground bounce to decrease noise delays.These transceivers implement a unique digital and analogimplementation to eliminate the delays and noiseinherent in traditional digital designs. The device offers anew method for quickly charging up a bus load capacitorto minimize bus settling times, or FastBus™ Charge.FastBus Charge is a transition current, (specified asIDYNAMIC) that injects between 60 to 200mA (dependingon output load) of current during the rise time and falltime. This current of ML65F16244 is used to reduce the amount of time ittakes to charge up a heavily-capacitive loaded bus,effectively reducing the bus settling times, andimproving data/clock margins in tight timing budgets.

Micro Linear's solution is intended for applications forcritical bus timing designs that include minimizingdevice propagation delay, bus settling time, and timedelays due to noise. Applications include; high speedmemory arrays, bus or backplane isolation, bus to busbridging, and sub-2ns propagation delay schemes.

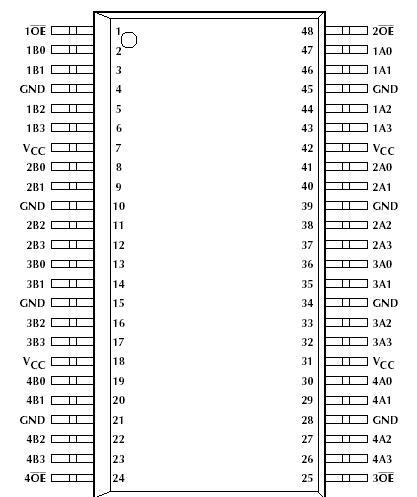

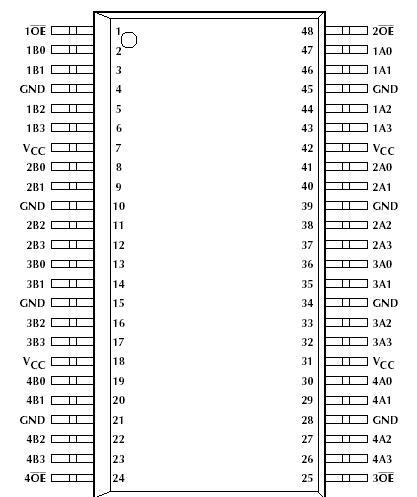

The ML65F16244 follows the pinout and functionality ofthe industry standard 2.7V to 3.6V-logic families.

ML65F16244 Data Sheet

ML65F16244 Data Sheet