Features: The controller implements the complete requirements of the IEEE 8961 specification as a subset of its fea-tures

Supports Arbitration message sending and receiving

Supports the two modes of operation (RESTRICTED/UNRESTRICTED)

Software configurable doublesingle pass operation slowfast IBAParking and restrictedunrestricted modes of arbitration

Built-in 1 ms timer for use in the arbitration cycle

User programmable 16 arbitration delays (8 slow and 8 fast)

Built-in PLL for accurate delays The PLL accepts clocks from 2 MHz to 40 MHz in steps of 1 MHz

Signal to unlock slave modules on transfer of tenure Auto unlock through a dummy cycle if the current mas-ter locked resources

Programmable delay for releasing ar* after issuing COMPETEIBA CMPT This is to ensure the assertion of the arbitration number during competition before the release of ar Also this delay ensures there is suffi-cient time to assert the ADDATA lines during Idle Bus Arbitration before the release of ar*

ReadWrite facility with data acknowledge for the host to load arbitration numbers an arbitration message and control registers

On chip parity generator unloads the host of the addi-tional parity generation function

Separate interrupts to indicate error occurrence and ar-bitration message received Interrupts cleared on a reg-ister write Error status is available in a separate status register

A special output pin to indicate that a POWERFAIL message was received

Hardwired register to hold the first word of the arbitra-tion message

FIFO strobe provided to store more than one arbitration message externally to prevent overrun

Idle Bus Arbitration (IBA) supported

Parking implemented

Bus initialization system reset and Live-insertion sup-ported (The logic to detect these conditions must be implemented externally)

Testability in the form of reading from key registers which include the STATE MCW 1 ms timer and pro-grammable input clock divider

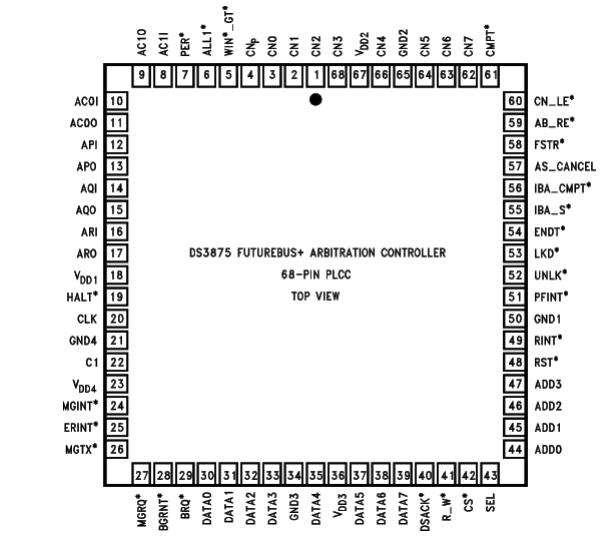

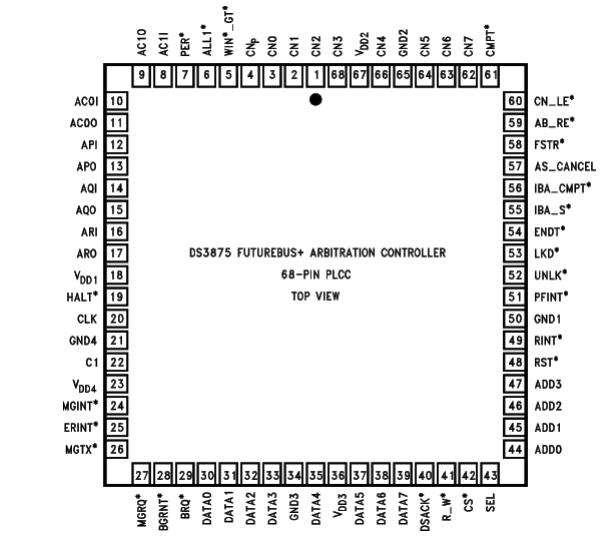

Pinout SpecificationsIf MilitaryAerospace specified devices are required please contact the National Semiconductor Sales OfficeDistributors for availability and specifications

SpecificationsIf MilitaryAerospace specified devices are required please contact the National Semiconductor Sales OfficeDistributors for availability and specifications

SupplyVoltage 6.5V

ControlInputVoltage 5.5V

PowerDissipationat70 0.6W

StorageTemperatureRange -65to+150

LeadTemperature 260DescriptionThe DS3875 Futurebus+ Arbitration Controller is a member of National Semiconductor's Futurebus +chip set designed specifically for the IEEE 8961 Futurebus +standard The DS3875 implements Distributed Arbitration and Distributed Arbitration messages in a single chip.

The DS3875 interfaces with Futurebus +through the DS3885 BTL Arbitration Transceiver and the DS3884A BTL Handshake Transceiver The DS3885 BTL Arbitration Transceiver incorporates the competition logic needed for the Arbitration Number signal lines The DS3884A BTL Handshake Transceiver has selectable Wired-OR receiver glitch filtering The DS3884A is used for the Arbitration Se-quencing and Arbitration Condition signal lines .

Additional transceivers included in the Futurebus +chip set are the DS3883A BTL 9-bit Data Transceiver and the DS3886A BTL 9-bit Latching Data Transceiver The DS3886A transceiver features edge-triggered latches in the driver which may be bypassed during a fall-through mode and a transparent latch in the receiver The DS3883A trans-ceiver has no latches in either direction.

The Logical Interface Futurebus +Engine (LIFE) IO Proto-col Controller with 64-bit Data Path incorporates the Com-pelled Mode Futurebus Parallel Protocol The Protocol Controller handles all the handshaking signals between the Futurebus +and the local bus interfaces and incorporates a DMA Controller with built-in FIFOs for fast queueing.

DS3875 Data Sheet

DS3875 Data Sheet