Features: ` Industrial and commercial temperatures

` Organization:131,027 words x8 bits

`High speed

- 10/12/15/20 ns address access time

- 5, 6, 7, 8 ns output enable access time

` Low power consumption: ACTIVE

- 605mW / max @ 10 ns

` Low power consumption: STANDBY

- 55 mW / max CMOS

` 6 T 0.18 u CMOS technology

` Easy memory expansion with CE , OE inputs

` Center power and ground

` TTL/LVTTL-compatible, three-state I/O

` JEDEC standard packaging

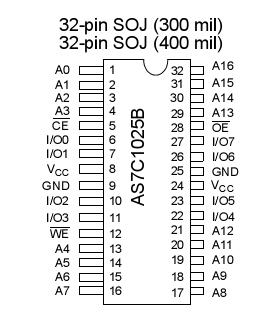

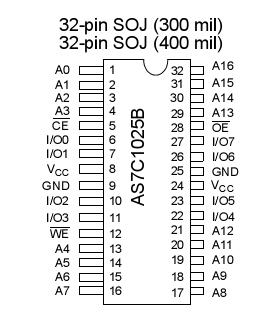

- 32-pin 300 mil SOJ

- 32-pin 400 mil SOJ

` ESD protection 2000 volts

`Latch-up current 200 mA

Pinout Specifications

Specifications

| Parameter |

Symbol |

Min |

Max |

Unit |

| Voltage on VCC relative to GND |

Vt1 |

-0.50 |

+7.0 |

V |

| Voltage on any I/O pin relative to GND |

Vt2 |

0.50 |

VCC+ 0.50 |

V |

| Power dissipation |

PD |

|

1.0 |

W |

| Storage temperature (plastic) |

Tstg |

65 |

+150 |

|

Temperature with VCC applied

|

Tbias |

55 |

+125 |

|

| DC output current (low) |

IOUT |

|

20 |

mA |

DescriptionThe AS7C1025B are high-performance CMOS 1,048,576-bit Static Random Access Memory (SRAM) devices organized as 131,072 words x 8 bits. They are designed for memory applications where fast data access, low power, and simple interfacing are desired.

Equal address access of AS7C1025B-12TJIN and cycle times (tAA, tRC, tWC) of 10/12/15/20 ns with output enable access times (tOE) of 3/3/4/5 ns are ideal for high-performance applications.The chip enable input CE permits easy memory and expansion with multiple-bank memory systems.

When CE is high the devices enter stanby mode. The AS7C1025A is guaranteed not to exceed 55 mW power consumption in CMOS standby mode. The devices also offer 2.0V data retention.

A write cycle is accomplished by asserting write enable (WE ) and chip enable (CE). Data on the input pins I/O0I/O7 is written on the rising edge of WE (write cycle 1) or CE (write cycle 2). To avoid bus contention, external devices should drive I/O pins only after outputs have been disabled with output enable (OE ) or write enable (WE ).

A read cycle is accomplished by asserting output enable (OE ) and chip enable (CE), with write enable (WE ) high. the chips drive I/O pins with the data word referenced by the input address. When either chip enable or output enable is inactive, or write enable is active, output drivers stay in high-impedance mode.

All chip inputs and outputs are TTL-compatible, and operation is from a single 5 V supply. The AS7C1025B is packaged in common industry standard packages.

AS7C1025B-12TJIN Data Sheet

AS7C1025B-12TJIN Data Sheet