Features: JEDEC standard 3.3V power supply

LVTTL compatible with multiplexed address

Dual banks / Pulse RAS

MRS cycle with address key programs

- CAS Latency (2,3)

- Burst Length (1,2,4,8 & full page)

- Burst Type (Sequential & Interleave)

All inputs are sampled at the positive going edge of the system clock

Industrial operating temperature range: -40oC to +85oC for -U

Burst Read Single-bit Write operation

DQM for masking

Auto & self refresh

32ms refresh period (2K cycle)

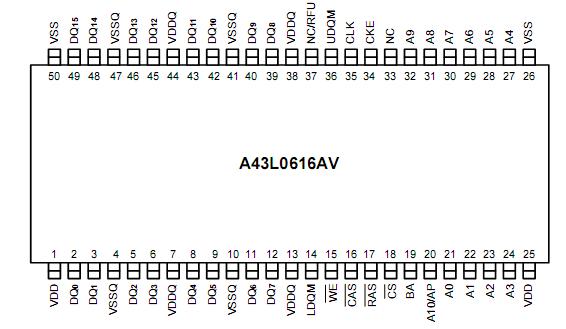

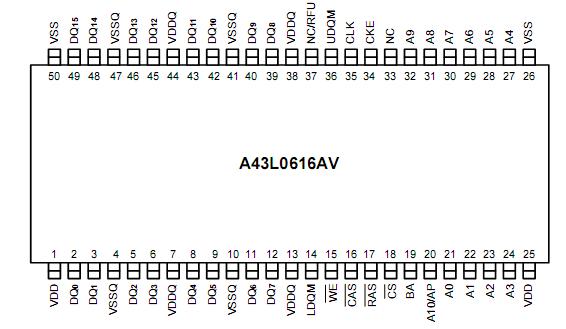

50 Pin TSOP (II)

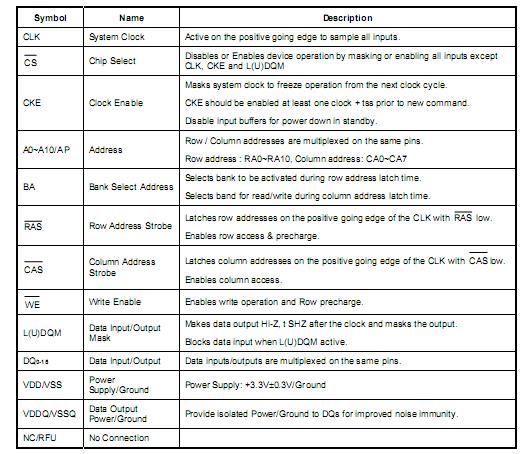

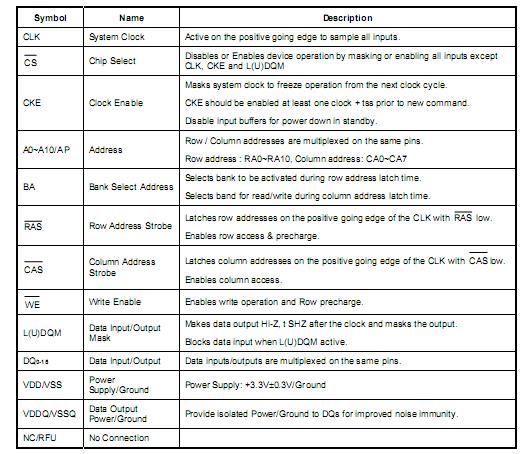

Pinout

Specifications

SpecificationsVoltage on any pin relative to VSS (Vin, Vout ) . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -1.0V to +4.6V

Voltage on VDD supply relative to VSS (VDD, VDDQ )

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -1.0V to +4.6V

Storage Temperature (TSTG) . . . . . . . . . . -55C to +150C

Soldering Temperature X Time (TSLODER) . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260C X 10sec

Power Dissipation ( PD) . . . . . . . . . . . . . . . . . . . . . . . . . 1W

Short Circuit Current (Ios) . . . . . . . . . . . . . . . . . . . . 50mA

DescriptionThe A43L0616A is 16,777,216 bits synchronous high data rate Dynamic RAM organized as 2 X 524,288 words by 16 bits, fabricated with AMIC,s high performance CMO technology. Synchronous design allows precise cycle control with the use of system clock. I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable latencies allows the same device A43L0616A to be useful for a variety of high bandwidth, high performance memory system applications.

A43L0616A Data Sheet

A43L0616A Data Sheet