Features: • Metastable immune characteristics

• Output skew guaranteed less than 1.5ns

• High source current (IOH = 15mA) ideal for clock driver applications

• Pin out compatible with 74F74

• 74F50728 for synchronizing cascaded Dtype flipflop

• See 74F50729 for synchronizing dual Dtype flipflop with edgetriggered set and reset

• See 74F50109 for synchronizing dual JK positive edgetriggered flipflop

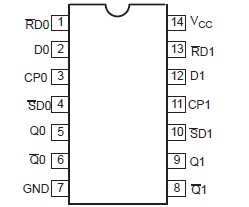

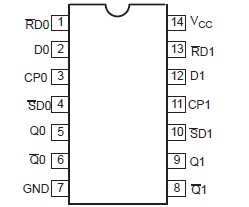

• Industrial temperature range available (40°C to +85°C)Pinout Description

DescriptionThe 74F5074 is a dual positive edgetriggered Dtype featuring individual data, clock, set and reset inputs; also true and complementary outputs.

Set (SD n) and reset (RD n) are asynchronous active low inputs and operate independently of the clock (CPn) input. Data must be stable just one setup time prior to the lowtohigh transition of the clock for guaranteed propagation delays.

Clock triggering of the 74F5074 occurs at a voltage level and is not directly related to the transition time of the positivegoing pulse. Following the hold time interval, data at the Dn input may be changed without affecting the levels of the output.

The 74F5074 is designed so that the outputs can never display a metastable state due to setup and hold time violations. If setup time and hold time are violated the propagation delays may be extended beyond the specifications but the outputs will not glitch or display a metastable state. Typical metastability parameters for the 74F5074 are: t

135ps and T

o

9.8 X 10

6 sec where t represents a function of the rate at which a latch in a metastable state resolves that condition and T

0 represents a function of the measurement of the propensity of a latch to enter a metastable state.

74F5074 Data Sheet

74F5074 Data Sheet

135ps and To

135ps and To  9.8 X 106 sec where t represents a function of the rate at which a latch in a metastable state resolves that condition and T0 represents a function of the measurement of the propensity of a latch to enter a metastable state.

9.8 X 106 sec where t represents a function of the rate at which a latch in a metastable state resolves that condition and T0 represents a function of the measurement of the propensity of a latch to enter a metastable state.