Features: • Output frequency up to 125 MHz

• 12 clock outputs: frequency configurable

• 350 ps max output-to-output skew

• Configurable output disable

• Two reference clock inputs for dynamic toggling

• Oscillator or PECL reference input

• Spread spectrum-compatible

• Glitch-free output clocks transitioning

• 3.3V power supply

• Pin-compatible with MPC973

• Industrial temperature range: 40 to +85

• 52-pin TQFP package

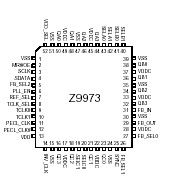

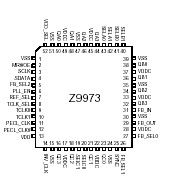

Pinout Specifications

SpecificationsMaximum Input Voltage Relative to VSS: ............. VSS 0.3V

Maximum Input Voltage Relative to VDD: ..............VDD + 0.3V

Storage Temperature: .................................65to + 150

Operating Temperature: ................................40 to +85

Maximum ESD protection .................................................2 kV

Maximum Power Supply: .................................................5.5V

Maximum Input Current:............................................±20 mA

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, VIN and VOUT should be constrained to the range:

VSS < (VIN or VOUT) < VDD .

Unused inputs must always be tied to an appropriate logic voltage level (either VSS or VDD).

DescriptionThe Z9973 has an integrated PLL that provides low-skew and low-jitter clock outputs for high-performance microprocessors. Three independent banks of four outputs as well as an independent PLL feedback output, FB_OUT, provide exceptional flexibility for possible output configurations. The PLL is ensured stable operation given that the VCO is configured to run between 200 MHz to 480 MHz. This allows a wide range of output frequencies up to125 MHz.

The phase detector compares the input reference clock to the external feedback input. For normal operation, the external feedback input, FB_IN, is connected to the feedback output, FB_OUT. The internal VCO is running at multiples of the input reference clock set by FB_SEL(0:2) and VCO_SEL select inputs (see Table 1). The VCO frequency is then divided to provide the required output frequencies. These dividers are set by SELA(0,1), SELB(0,1), SELC(0,1) select inputs (see Table 2). For situations in which the VCO needs to run at relatively low frequencies and hence might not be stable, assert VCO_SEL LOW to divide the VCO frequency by 2. This will maintain the desired output relationships, but will provide an enhanced PLL lock range.

The Z9973 is also capable of providing inverted output clocks. When INV_CLK is asserted HIGH, QC2 and QC3 output locks are inverted. These clocks could be used as feedback outputs to the Z9973 or a second PLL device to generate early or late clocks for a specific design. This inversion does not affect the output to output skew.

Z9973 Data Sheet

Z9973 Data Sheet