Features: • Compatible With 1394 Trade Association's Digital Camera Specification, Draft 1.04

• 1394a Link Layer Controller With 400 Mbits/s Capability

• Support for Several CCD Sensors

Sony ICX084AK, ICX098AK

Sharp LZ24BP

Texas Instruments TC237

• Integrated CCD (Charge-Coupled Device) and CDS (Correlated Double Sampling) Pulse Timer With Programmable Pulse Skew

• Video Controls

Brightness (Auto/Manual)

Exposure (Auto/Manual)

Sharpness (Manual)

Saturation (Manual)

White Balance (Auto/Manual)

Gamma (Manual)

Backlight Compensation (Manual)

• Three Stepper Motor Controls for Focus/Zoom/Tilt or Other Motorized Functions

• EEPROM Interface

• Programmable Status/Test Terminals

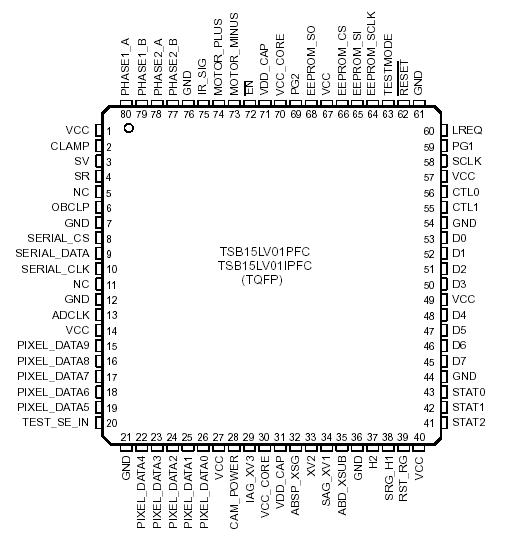

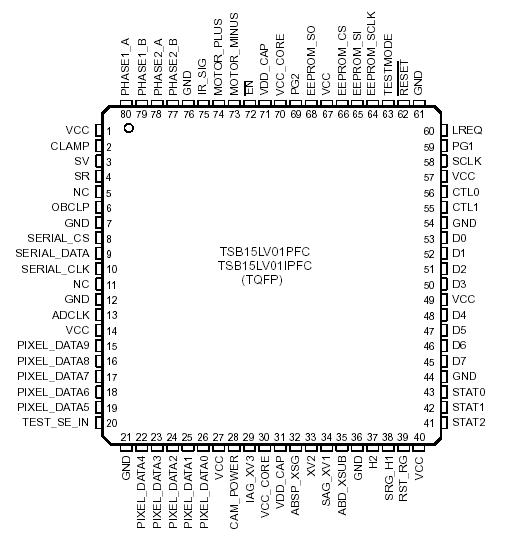

• Seamlessly Connects to TI's 1394 Physical Layer DevicesPinout SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 4 V

SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 4 V

Input voltage range, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to VCC + 0.5 V

Output voltage range, VO . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to VCC + 0.5 V

Input clamp current, IIK (VI < 0 or VI > VCC (see Note 1) . . . . . . . . . . . . ±20 mA

Output clamp current, IOK (VO < 0 or VO > VCC (see Note 2) . . . . . . . . . ±20 mA

Operating free-air temperature range (no suffix) . . . . . . . . . . . . . . . . .0 to 70

("I" suffix) . . . . . . . . . . . . .40 to 85

Storage temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . 65 to 150

Virtual junction temperature, TJ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . 150 NOTES:

1. This applies to external input and bidirectional buffers.

2. This applies to external output and bidirectional buffers.

DescriptionThe timing of these interfaces takes into consideration two asynchronous, periodic events. The first event is the integration of light in the sensor, which occurs at a frequency dictated by the camera's frame rate. The second event

is the beginning of a 1394 isochronous cycle, which determines when video data is transmitted from the TSB15LV01.

The TSB15LV01 reconciles these two events in a way that produces optimal video quality while minimizing the amount of memory necessary to store the pixel data.

When the integration cycle is complete, the pixel charges are transferred out of the active region of the sensor. For the TC237, which is a full frame transfer CCD, this is the parallel transfer of charge from the image area to the storage

area. For the other sensors, which are interline CCDs, this is the transfer of charge to the vertical shift registers. Several dummy/black lines are subsequently clocked and processed by the AFE.

At this point, timing waits for the next 1394 isochronous cycle. As data is clocked out onto the serial bus, more data is needed and therefore clocked out of the sensor and into the TSB15LV01. This method of processing reconciles the two asynchronous, periodic events. It also minimizes the size of the internal FIFO needed to buffer the data stream, since data is only taken from the CCD as it is needed.

The data is packetized on the bus such that there is a period of time between frames in which no data remains to be clocked out of the sensor, and no data is being transferred on the serial bus. During such periods of inactivity, the TSB15LV01 may clock pixels out of the serial register while ignoring the resulting processed data from the AFE. This results in lines of blank dummy pixels being clocked out of the CCD at regular intervals. This action is taken because extended idle periods can allow the CCD serial register to accumulate dark current. Clocking these pixels also keeps a constant dc level at the AFE ac-coupling capacitor.

Figures 2-4 through 2-12 show the sensor interface for each approved sensor. For each sensor, there are four views shown. The first view contains the timing for the acquisition and transfer of a full frame of video. The second view is a magnified portion of the start frame. The third view is a magnified portion of the start of a line, while the fourth view is a magnified portion of the horizontal drive pulses. In some cases, the pulses are identical for the different sensoroptions, so they are consolidated under a single figure. In all figures, the mode is YUV 4:1:1 640 x 480, at 30 frames per second, with minimum exposure time.

Note that these signals are intended to be processed by one of the recommended driver devices before reaching the CCD. In addition to level-shifting, these devices perform logic on the signals. Therefore, the signals at the sensor are different than the ones shown in Figures 2-4 through 2-12.

TSB15LV01 Data Sheet

TSB15LV01 Data Sheet