Features: • Supports provisions of IEEE 1394-1995 Standard for High-Performance Serial Bus

• Interoperable with FireWireE implementation of the 1394 standard

• Interfaces directly to Texas Instruments TSB11LV01 and TSB21LV03A physical layer (Phy) devices (100/200Mbits/s)

• Multimode 8-/16-bit microcontroller/microprocessor interface supports many processors

• Interrupt driven to minimize host polling

• 8K-byte FIFO supports fully bidirectional MPEG2/DSS, asynchronous, and isochronous modes for transmit and receive

• 64 quadlet (256-Byte) control FIFO accessed through microcontroller interface supports command/status operations

• Supports bus functions and automatic 1394 Self-ID verification

• Single 3.3-V supply operation with 5-V tolerance using 5-V bias terminals

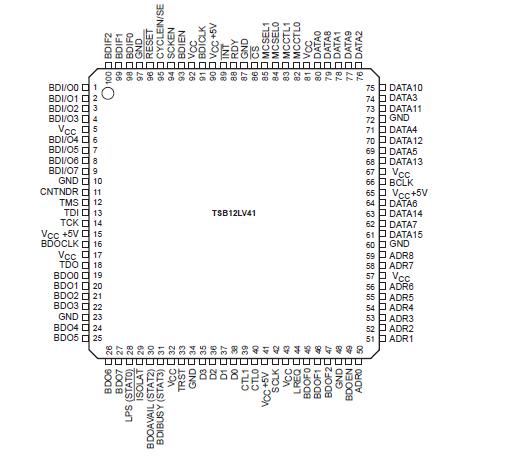

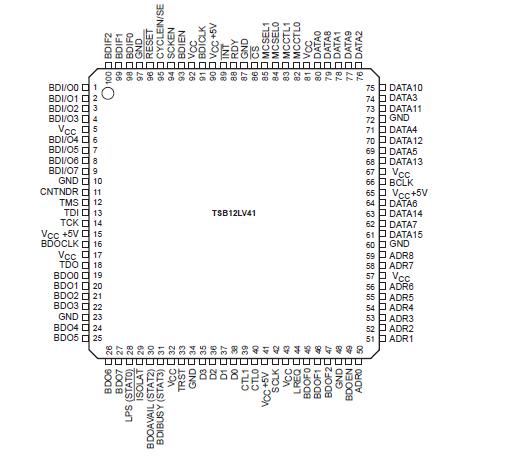

• High-performance 100-Pin PZ (S-PQFP-G100) package

Pinout SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 3.6 V

SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 3.6 V

Supply voltage range, VCC5V . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 5.5 V

Input voltage range, VI . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to VCC5V + 0.5 V

Output voltage range, VO . . . . . . . . . . . . . . . . . . . . . . 0.5 V to VCC5V + 0.5 V

Input clamp current, IIK (VI < 0 V or VI > VCC) (see Note 1) . . . . . . . . . ±20 mA

Output clamp current, IOK (VO < 0 V or VO > VCC) (see Note 2) . . . . . . ±20 mA

Continuous total power dissipation, PD . . . . . . . . (see dissipation rating table)

Operating free-air temperature range, TA . . . . . . . . . . . . . . . . . . .. 0°C to 70°C

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . .65°C to 150°C

NOTES:

1. This parameter applies to external input and bidirectional buffers. For 5-V tolerant terminals use

VI > VCC5V.

2. This parameter applies to external output and bidirectional buffers. For 5-V tolerant terminals use

VO > VCC5V.DescriptionThe Texas Instruments TSB12LV41 link-layer controller (LLC) (also called MPEG2Lynx) complies with the IEEE 1394-1995 (from here on referred to as 1394) specification for high-performance serial bus, transmits and receives correctly-formatted 1394 packets, detects lost cycle-start packets, and generates and inspects the 32-bit cyclic redundancy check (CRC). The TSB12LV41 is also capable of performing the functions of cycle master (CM), isochronous resource manager (IRM), and bus manager (BM). Support is provided for the IEC61883 standard for transmitting MPEG2 compressed video on 1394, with automatic generation of the common isochronous packet headers and timestamping as required by the IEC 61883 standard. The TSB12LV41 provides a 1394 interface for high-performance audio, video, and data applications at up to 200 Mbits/s. It is suitable for set-top boxes, multimedia tape, disk drives, and other consumer electronic devices requiring MPEG-2 formatted isochronous data transfer according to the IEC61883 specification. The TSB12LV41 also supports non-MPEG-2/DSS isochronous and asynchronous data transfer with an auto-packetization feature.

The TSB12LV41 interfaces directly to several microprocessors and microcontrollers, including embedded ARM processor, Intel 8051 and the Motorola 68000. The microprocessor interface supports both 8-bit and 16-bit data busses. It can also automatically transform addresses to interface to either big endian or little endian type processors.

The bulky data interface (BDIF) is a 16-bit wide I/O port that enables both transmit and receive of DVB/DSS, isochronous, and asynchronous data. This port is full-duplex, meaning it is capable of transmitting and receiving 1394 packets simultaneously. A separate 8K-byte FIFO, accessible via the bulky data interface, provides logically independent FIFOs for transmit and receive of isochronous, asynchronous, and MPEG2 compressed DVB/DSS data. The 8K-byte FIFO or bulky data FIFO can perform asynchronous packet transmit retry up to 256 times with intervals up to 256 × 125 ms. The TSB12LV41 supports full-width time-stamped offsets for MPEG2 compressed DVB/DSS transmit and receive, and also performs age filtering functions. A 256-byte FIFO is used to transmit and receive asynchronous control packets.

TSB12LV41 Data Sheet

TSB12LV41 Data Sheet