Features: • Compliant With IEEE 1394-1995 Standards and P1394a Supplement for High Performance Serial Bus†

• Supports Transfer Rates of 400, 200, or 100 Mbit/s

• Compatible With Texas Instruments Physical Layer Controllers (Phys)

• Supports the Texas Instruments Bus Holder Galvanic Isolation Barrier

• Glueless Interface to 68000 and ColdFire Microcontrollers/Microprocessors

• Supports ColdFire Burst Transfers

• 2K-Byte General Receive FIFO (GRF) Accessed Through Microcontroller Interface Supports Asynchronous and Isochronous Receive

• 2K-Byte Asynchronous Transmit FIFO (ATF) Accessed Through Microcontroller Interface Supports Asynchronous Transmissions

• Programmable Microcontroller Interface With 8-Bit or 16-Bit Data Bus, Multiple Modes of Operation Including Burst Mode, and Clock Frequency to 60 MHz.

• 8-Bit or 16-Bit Data Mover Port (DM Port) Supports Isochronous, Asynchronous, and Streaming Transmit/Receive From an Unbuffered Port at a Clock Frequency of 25 MHz.

• Backward Compatible With All TSB12LV31(GPLynx) Microcontroller and Data Mover Functionality in Hardware.

• Four-Channel Support for Isochronous Transmit From Unbufferred 8/16 Bit Data Mover Port.

• Single 3.3-V Supply Operation With 5-V Tolerance Using 5-V Bias Terminals.

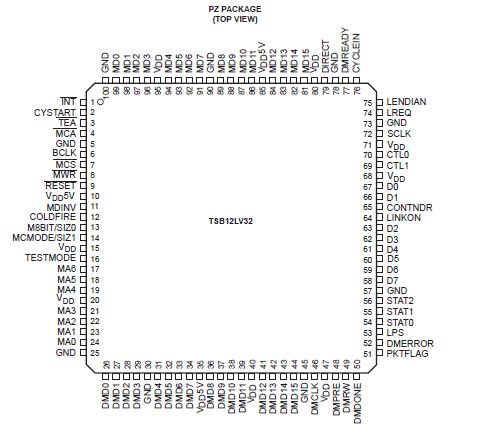

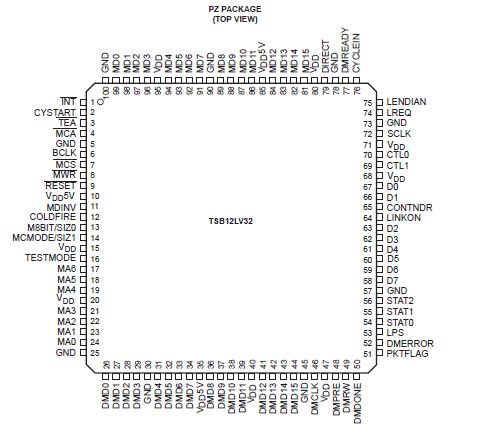

• High Performance 100-Pin PZ Package

Pinout SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 3.6 V

SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 3.6 V

Supply voltage range, VCC5V . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 5.5 V

Input voltage range, VI . . . . . . . . . . . . . . . . . . . . .0.5 V to VCC5V + 0.5 V

Output voltage range, VO . . . . . . . . . . . . . . . . . . .0.5 V to VCC5V + 0.5 V

Input clamp current, IIK (VI < 0 or VI > VCC . . . . . . . . . . . . . . . . . . ±20 mA

Output clamp current, IOK (VO < 0 or VO > VCC . . . . . . . . . . . . . . . ±20 mA

Operating free-air temperature range: TSB12LV32 . . . . . . . 0°C to 70°C

Operating free-air temperature range: TSB12LV32I . . . . . 40°C to 85°C

Storage temperature range . . . . . . . . . . . . . . . . . . . . . . .65°C to 150°C

NOTES:

1. This applies to external input and bidirectional buffers. For 5-V tolerant terminals, use VI > VCC5V.

2. This applies to external output and bidirectional buffers. For 5-V tolerant terminals, use VI > VCC5V.DescriptionThe TSB12LV32 (GP2Lynx) is a high-performance general-purpose IEEE P1394a link-layer controller (LLC) with the capability of transferring data between a host controller, the 1394 Phy-link interface, and external devices connected to the data mover port (local bus interface). The 1394 Phy-link interface provides the connection to the 1394 physical layer device and is supported by the LLC. The LLC provides the control for transmitting and receiving 1394 packet data between the microcontroller interface and the Phy-link interface via internal 2K byte FIFOs at rates up to 400 Mbit/s. The TSB12LV32 transmits and receives correctly formatted 1394 packets, generates and detects the 1394 cycle start packets, communicates transaction layer transmit requests to the Phy, and generates and inspects the 32-bit cyclic redundancy check (CRC). The TSB12LV32 is capable of being cycle master (CM), isochronous resource manager (IRM), bus manager, and supports reception of isochronous data on two channels.

The TSB12LV32 supports a direct interface to many microprocessors/microcontrollers including programmable endian swapping. TSB12LV32 has a generic 16/8-bit host bus interface which includes support for the ColdFireE microcontroller mode at rates up to 60 MHz. The microinterface may operate in byte or word (16 bit) accesses. The data mover block in GP2Lynx is meant to handle an external memory interface of large data blocks. The port can be configured to either transmit or receive data packets. The packets can be either asynchronous, isochronous, or streaming data packets. Asynchronous or isochronous receive packets will be routed to the DM port or the GRF via the receiver routing control logic. The internal FIFO is separated into a transmit FIFO and a receive FIFO each of 517 quadlets (2 Kbytes). Asynchronous packets may be transmitted from the DM port or the internal FIFO. If there is contention the FIFO has priority and will be transmitted first.

The LLC also provides the capability to receive status information from the physical layer device and to access the physical layer control and status registers by the application software.

TSB12LV32I Data Sheet

TSB12LV32I Data Sheet