Features: ` High-Performance Static CMOS Technology

` TMS470R1x 16/32-Bit RISC Core (ARM7TDMI™)

60-MHz System Clock (Pipeline Mode)

Independent 16/32-Bit Instruction Set

Open Architecture With Third-Party Support

Built-In Debug Module

` Integrated Memory (VF48C only)

1M-Byte Program Flash

Two Banks With 16 Contiguous Sectors

64K-Byte Static RAM (SRAM)

Memory Security Module (MSM)

JTAG Security Module

` Integrated Memory (VF48B only)

768K-Byte Program Flash

Two Banks With 12 Contiguous Sectors

48K-Byte Static RAM (SRAM)

Memory Security Module (MSM)

JTAG Security Module

` Operating Features

Low-Power Modes: STANDBY and HALT

Industrial/Automotive Temperature Ranges

` 470+ System Module

32-Bit Address Space Decoding

Bus Supervision for Memory/Peripherals

Digital Watchdog (DWD) Timer

Analog Watchdog (AWD) Timer

Enhanced Real-Time Interrupt (RTI)

Interrupt Expansion Module (IEM)

System Integrity and Failure Detection

ICE Breaker

` Direct Memory Access (DMA) Controller

32 Control Packets and 16 Channels

` Frequency-Modulated Zero-Pin Phase-Locked Loop (FMZPLL)-Based Clock Module With Prescaler

Multiply-by-8 Internal FMZPLL Option

ZPLL Bypass Mode

` Twelve Communication Interfaces:

Two Serial Peripheral Interfaces (SPIs)

255 Programmable Baud Rates

Three Serial Communication Interfaces (SCIs)

224 Selectable Baud Rates

Asynchronous/Isosynchronous Modes

Two High-End CAN Controllers (HECC)

32-Mailbox Capacity

Fully Compliant With CAN Protocol,Version 2.0B

Five Inter-Integrated Circuit (I2C) Modules

Multi-Master and Slave Interfaces

Up to 400 Kbps (Fast Mode)

7- and 10-Bit Address Capability

High-End Timer Lite (HET)

12 Programmable I/O Channels:

12 High-Resolution Pins

High-Resolution Share Feature (XOR)

High-End Timer RAM

64-Instruction Capacity

` External Clock Prescale (ECP) Module

Programmable Low-Frequency External Clock (CLK)

` 12-Channel 10-Bit Multi-Buffered ADC (MibADC)

64-Word FIFO Buffer

Single- or Continuous-Conversion Modes

1.55 s Minimum Sample and Conversion Time

Calibration Mode and Self-Test Features

` Flexible Interrupt Handling

` Expansion Bus Module (EBM)

Supports 8- and 16-Bit Expansion Bus Memory Interface Mappings

42 I/O Expansion Bus Pins

` 46 Dedicated General-Purpose I/O (GIO) Pins and 47 Additional Peripheral I/Os

` Sixteen External Interrupts

` Compatible ROM Device (Planned)

` On-Chip Scan-Base Emulation Logic,IEEE Standard 1149.1(1) (JTAG) Test-Access Port

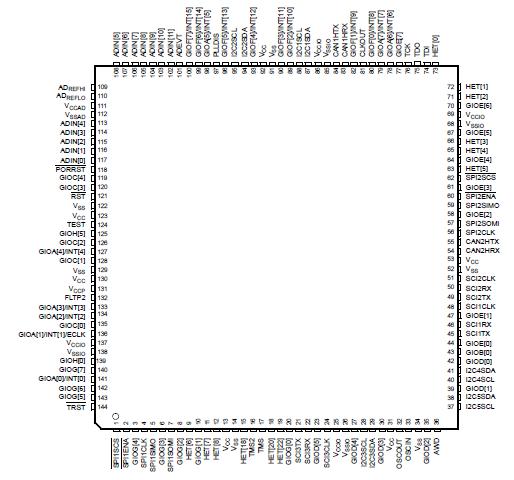

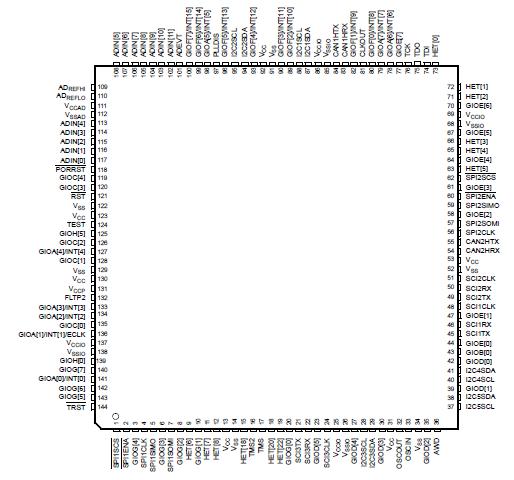

` 144-Pin Plastic Low-Profile Quad Flatpack (PGE Suffix)

` Development System Support Tools Available

Code Composer Studio™ Integrated Development Environment (IDE)

HET Assembler and Simulator

Real-Time In-Circuit Emulation

Flash ProgrammingApplication·Audio

·Automotive

·Broadband

·Digital Control

·Military

·Optical Networking

·Security

·Telephony

·Video & Imaging

·WirelessPinout Specifications

SpecificationsSupply voltage ranges: VCC(2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .−0.3 V to 2.5 V

Supply voltage ranges: VCCIO, VCCAD, VCCP (flash pump)(2) . . . . . . . . . . . .−0.3 V to 4.1 V

Input voltage range: All 5 V tolerant input pins. . . . . . . . . . . . . . . . . . . . . . −0.3 V to 6.0 V

All other input pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .−0.3 V to 4.1 V

Input clamp current: All 5 V tolerant pins,PORRST, TRST, TEST and TCK (VI < 0) . . . .−20mA

ADIN[0:11] IIK (VI < 0 or VI > VCCAD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10 mA

All other pins IIK (VI < 0 or VI > VCCIO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±20 mA

Operating free-air temperature ranges, TA: A version . . . . . . . . . . . . . . . .40°C to 85°C

T version . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .−40°C to 105°C

Q version . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .−40°C to 125°C

Operating junction temperature range, TJ . . . . . . . . . . . . . . . . . . . . . . . . 40°C to 150°C

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .−40°C to 150°C

1 Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only,and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2 All voltage values are with respect to their associated grounds.

DescriptionThe TMS470R1VF48B devices are members of the Texas Instruments TMS470R1x family of general-purpose 16/32-bit reduced instruction set computer (RISCllers. The VF48x microcontroller offers high performance utilizing the high-speed ARM7TDMI 16/32-bit RISC central processing unit (CPU), resulting in a high instruction throughput while maintaining greater code efficiency. The ARM7TDMI 16/32-bit RISC CPU views memory as a linear collection of bytes numbered upwards from zero. The VF48x uses the big-endian format where the most significant byte of a word is stored at the lowest numbered byte and the least significant byte at the highest numbered byte.

High-end embedded control applications demand more performance from their controllers while maintaining low costs. The VF48x RISC core architecture offers solutions to these performance and cost demands while maintaining low power consumption.

The VF48x devices contain the following:

`ARM7TDMI 16/32-Bit RISC CPU

`TMS470R1x system module (SYS) with 470+ enhancements

`1M-byte flash (VF48C only)

`768K-byte flash (VF48B only)

`64K-byte SRAM (VF48C only)

`48K-byte SRAM (VF48B only)

`Frequency-modulated zero-pin phase-locked loop (FMZPLL) clock module

`Digital watchdog (DWD) timer

`Analog watchdog (AWD) timer

`Enhanced real-time interrupt (RTI) module

`Interrupt expansion module (IEM)

`Memory security module (MSM)

`JTAG security module

`Two serial peripheral interface (SPI) modules

`Three serial communications interface (SCI) modules

`Two high-end CAN controllers (HECC)

`Five inter-integrated circuit (I2C) modules

`10-bit multi-buffered analog-to-digital converter (MibADC), with 12 input channels

`High-end timer lite (HET) controlling 12 I/Os

`External Clock Prescale (ECP)

`Expansion Bus Module (EBM)

`Up to 93 I/O pins

The functions performed by the 470+ system module (SYS) include:

`Address decoding

`Memory protection

`Memory and peripherals bus supervision

`Reset and abort exception management

`Prioritization for all internal interrupt sources

`Device clock control

`Parallel signature analysis (PSA)

The enhanced real-time interrupt (RTI) module on the VF48x has the option to be driven by the oscillator clock.

The digital watchdog (DWD) is a 25-bit resettable decrementing counter that provides a system reset when the watchdog counter expires. This data sheet includes device-specific information such as memory and peripheral select assignment, interrupt priority, and a device memory map. For a more detailed functional description of the SYS module, see the TMS470R1x System Module Reference Guide (literature number SPNU189).

The VF48x memory includes general-purpose SRAM supporting single-cycle read/write accesses in byte,half-word, and word modes.

The flash memory on this device is a nonvolatile, electrically erasable and programmable memory implemented with a 32-bit-wide data bus interface. The flash operates with a system clock frequency of up to 24 MHz. When in pipeline mode, the flash operates with a system clock frequency of up to 60 MHz. For more detailed information on the flash, see the flash section of this data sheet and the TMS470R1x F05 Flash Reference Guide (literature number SPNU213).

The memory security module (MSM) and the JTAG security module prevent unauthorized access and visibility to on-chip memory, thereby preventing reverse engineering or manipulation of proprietary code. For more detailed information, see the TMS470R1x Memory Security Module Reference Guide (literature number SPNU246) and the TMS470R1x JTAG Security Module Reference Guide (literature number SPNU245).

The VF48x device has twelve communication interfaces: two SPIs, three SCIs, two HECCs, and five I2Cs. The SPI provides a convenient method of serial interaction for high-speed communications between similar shiftregister type devices. The SCI is a full-duplex, serial I/O interface intended for asynchronous communication between the CPU and other peripherals using the standard non-return-to-zero (NRZ) format. The HECC uses a serial, multimaster communication protocol that efficiently supports distributed real-time control with robust communication rates of up to 1 megabit per second (Mbps). These CAN peripherals are ideal for applications operating in noisy and harsh environments (e.g., automotive and industrial fields) that require reliable serial communication or multiplexed wiring. The I2C module is a multi-master communication module providing an interface between the VF48x microcontroller and an I2C-compatible device via the I2C serial bus. The I2C supports both 100 Kbps and 400 Kbps speeds. For more detailed functional information on the SPI, SCI, and CAN peripherals, see the specific reference guides (literature numbers SPNU195, SPNU196, and SPNU197).

For more detailed functional information on the I2C, see the TMS470R1x Inter-Integrated Circuit (I2C) Reference Guide (literature number SPNU223).The HET is an advanced intelligent timer that provides sophisticated timing functions for real-time applications.

The timer is software-controlled, using a reduced instruction set, with a specialized timer micromachine and an attached I/O port. The HET can be used for compare, capture, or general-purpose I/O. It is especially well suited for applications requiring multiple sensor information and drive actuators with complex and accurate time pulses. The HET used in this device is the high-end timer lite. It has fewer I/Os than the usual 32 in a standard HET. For more detailed functional information on the HET, see the TMS470R1x High-End Timer (HET) Reference Guide (literature number SPNU199). The VF48x HET peripheral contains the XOR-share feature.

This feature allows two adjacent HET high- resolution channels to be XORed together, making it possible to output smaller pulses than a standard HET. For more detailed information on the HET XOR-share feature, see the TMS470R1x High-End Timer (HET) Reference Guide (literature number SPNU199).The VF48x device has one 10-bit-resolution, sample-and-hold MibADC. Each of the MibADC channels can be converted individually or can be grouped by software for sequential conversion sequences. There are three separate groupings, two of which can be triggered by an external event. Each sequence can be converted once when triggered or configured for continuous conversion mode. For more detailed functional information on the MibADC, see the TMS470R1x Multi-Buffered Analog-to-Digital Converter (MibADC) Reference Guide (literature number SPNU206).

The frequency-modulated zero-pin phase-locked loop (FMZPLL) clock module contains a phase-locked loop,a clock-monitor circuit, a clock-enable circuit, and a prescaler (with prescale values of 18). The function of the FMZPLL is to multiply the external frequency reference to a higher frequency for internal use. The FMZPLL provides ACLK to the system (SYS) module. The SYS module subsequently provides system clock (SYSCLK),real-time interrupt clock (RTICLK), CPU clock (MCLK), and peripheral interface clock (ICLK) to all other VF48x device modules. For more detailed functional information on the FMZPLL, see the TMS470R1x Frequency-Modulated Phase-Locked Loop (FMPLL) Clock Module Reference Guide (literature number SPNU221).

NOTE

ACLK should not be confused with the MibADC internal clock, ADCLK. ACLK is the continuous system clock from an external resonator/crystal reference.

The expansion bus module (EBM) is a standalone module that supports the multiplexing of the GIO functions and the expansion bus interface. For more information on the EBM, see the TMS470R1x Expansion Bus Module (EBM) Reference Guide (literature number SPNU222).

The VF48x device also has an external clock prescaler (ECP) module that when enabled, outputs a continuous external clock (ECLK) on a specified GIO pin. The ECLK frequency is a user-programmable ratio of the peripheral interface clock (ICLK) frequency. For more detailed functional information on the ECP, see the TMS470R1x External Clock Prescaler (ECP) Reference Guide (literature number SPNU202).

TMS470R1VF48B Data Sheet

TMS470R1VF48B Data Sheet