Features: High-Performance Static CMOS Technology

− 25-ns Instruction Cycle Time (40 MHz)

− 40-MIPS Performance

− Low-Power 3.3-V Design

Based on TMS320C2xx DSP CPU Core

− Code-Compatible With 240x and F243/F241/C242

− Instruction Set Compatible With F240/C240

On-Chip Memory

− Up to 8K Words x 16 Bits of Flash EEPROM (2 Sectors) (LF2401A)

− 8K Words x 16 Bits of ROM (LC2401A)

− Programmable "Code-Security" Feature for the On-Chip Flash/ROM

− Up to 1K Words x 16 Bits of Data/Program RAM

− 544 Words of Dual-Access RAM

− Up to 512 Words of Single-Access RAM

Boot ROM

− SCI Bootloader

Event-Manager (EV) Module (EVA), Which Includes:

− Two 16-Bit General-Purpose Timers

− Seven 16-Bit Pulse-Width Modulation (PWM) Channels Which Enable:

− Three-Phase Inverter Control

− Center- or Edge-Alignment of PWM Channels

− Emergency PWM Channel Shutdown With External PDPINTA Pin

− Programmable Deadband (Deadtime) Prevents Shoot-Through Faults

− One Capture Unit for Time-Stamping of External Events

− Input Qualifier for Select Pins

− Synchronized A-to-D Conversion

− Designed for AC Induction, BLDC, Switched Reluctance, and Stepper Motor Control

Small Foot-Print (7 mm * 7 mm) Ideally Suited for Space-Constrained Applications

Watchdog (WD) Timer Module

10-Bit Analog-to-Digital Converter (ADC)

− 5 Multiplexed Input Channels

− 500 ns Minimum Conversion Time

− Selectable Twin 8-State Sequencers Triggered by Event Manager

Serial Communications Interface (SCI)

Phase-Locked-Loop (PLL)-Based Clock Generation

Up to 13 Individually Programmable, Multiplexed General-Purpose Input/Output (GPIO) Pins

User-Selectable Dual External Interrupts (XINT1 and XINT2)

Power Management:

− Three Power-Down Modes

− Ability to Power Down Each Peripheral Independently

Real-Time JTAG-Compliant Scan-Based Emulation, IEEE Standard 1149.1† (JTAG)

Development Tools Include:

− Texas Instruments (TI) ANSI C Compiler, Assembler/Linker, and Code Composer Studio™ Debugger

− Evaluation Modules

− Scan-Based Self-Emulation (XDS510)

− Broad Third-Party Digital Motor Control Support

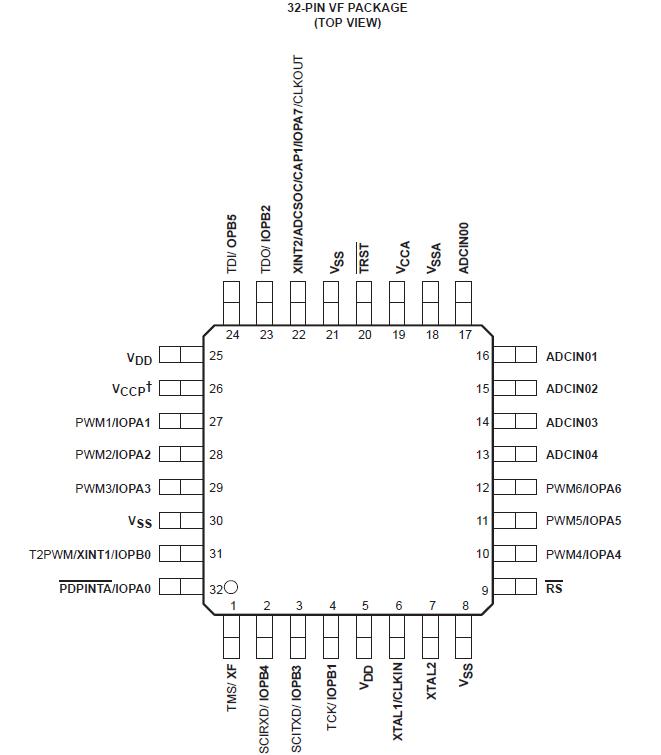

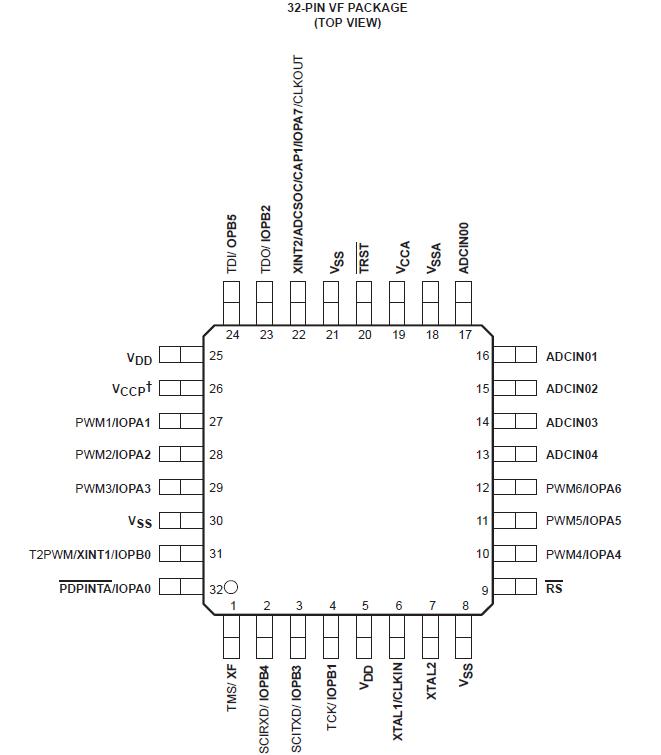

32-Pin VF Low-Profile Quad Flatpack (LQFP)

Temperature Range: − 40°C to 85°CPinout SpecificationsSupply voltage range, VDD, VDDO, and VCCA (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . − 0.3 V to 4.6 V

SpecificationsSupply voltage range, VDD, VDDO, and VCCA (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . − 0.3 V to 4.6 V

VCCP range (LF2401A) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . − 0.3 V to 5.5 V

Input voltage range, VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . − 0.3 V to 4.6 V

Output voltage range, VO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . − 0.3 V to 4.6 V

Input clamp current, IIK (VIN < 0 or VIN > VCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 20 mA

Output clamp current, IOK (VO < 0 or VO > VCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 20 mA

Operating case temperature range, TC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . − 40°C to 85°C

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . − 65°C to 150°C

† Clamp current stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to VSS.DescriptionThe TMS320LC2401A device, a new member of the TMS320C24x generation of digital signal processor (DSP) controllers, is part of the TMS320C2000 platform of fixed-point DSPs. The Lx2401A device offers the enhanced TMS320™ DSP architectural design of the C2xx core CPU for low-cost, low-power, and high-performance processing capabilities. Several advanced peripherals, optimized for digital motor and motion control applications, have been integrated to provide a true single-chip DSP controller. While code-compatible with the existing 240x and C24x™ DSP controller devices, the TMS320LC2401A offers increased processing performance (40 MIPS) and a higher level of peripheral integration. See the TMS320LC2401A Device Summary section for device-specific features.

The TMS320LC2401A device offers a peripheral suite tailored to meet the specific price/performance points required by various applications. The Lx2401A also offers a cost-effective reprogrammable solution for volume production. A password-based "code security" feature on the device is useful in preventing unauthorized duplication of proprietary code stored in on-chip Flash/ROM. Note that the TMS320LC2401A contains a 256-word boot ROM to facilitate in-circuit programming. The boot ROM on TMS320LC2401A is used for test purposes.

The TMS320LC2401A offers an event manager module which has been optimized for digital motor control and power conversion applications. Capabilities of this module include center- and/or edge-aligned PWM generation, programmable deadband to prevent shoot-through faults, and synchronized analog-to-digital conversion. Select EV pins have been provided with an "input-qualifier" circuitry, which minimizes inadvertent pin-triggering by glitches.

The high-performance, 10-bit analog-to-digital converter (ADC) TMS320LC2401A has a minimum conversion time of 500 ns and offers up to 5 channels of analog input. The autosequencing capability of the ADC allows a maximum of 16 conversions to take place in a single conversion session without any CPU overhead. A serial communications interface (SCI) is integrated on all devices to provide asynchronous communication to other devices in the system. To maximize device flexibility, functional pins are also configurable as general-purpose inputs/outputs (GPIOs).

To streamline development time, JTAG-compliant scan-based emulation has been integrated into all devices. This provides non-intrusive real-time capabilities required to debug digital control systems. A complete suite of code-generation tools from C compilers to the industry-standard Code Composer Studio™ debugger supports this family. Numerous third-party developers not only offer device-level development tools, but also system-level design and development support.

TMS320LC2401A Data Sheet

TMS320LC2401A Data Sheet