Features: ` Highest-Performance Floating-Point Digital Signal Processor (DSP): TMS320C6713

Eight 32-Bit Instructions/Cycle

32/64-Bit Data Word

225-, 150-MHz Clock Rate

4.4-, 6.7-ns Instruction Cycle Time

1800 MIPS/1350 MFLOPS, 1200 MIPS /900 MFLOPS

Rich Peripheral Set, Optimized for Audio

` VelociTITM Advanced Very Long Instruction Word (VLIW) TMS320C67x DSP Core

Eight Independent Functional Units:

Two ALUs (Fixed-Point)

Four ALUs (Floating- and Fixed-Point)

Two Multipliers (Floating- and Fixed-Point)

Load-Store Architecture With 32 32-Bit General-Purpose Registers

Instruction Packing Reduces Code Size

All Instructions Conditional

` Instruction Set Features

Native Instructions for IEEE 754

Single- and Double-Precision

Byte-Addressable (8-, 16-, 32-Bit Data)

8-Bit Overflow Protection

Saturation; Bit-Field Extract, Set, Clear; Bit-Counting; Normalization

` L1/L2 Memory Architecture

4K-Byte L1P Program Cache (Direct-Mapped)

4K-Byte L1D Data Cache (2-Way)

256K-Byte L2 Memory, With 64K-Byte L2 Unified Cache/Mapped RAM

192K-Byte Additional L2 Mapped RAM

` Device Configuration

Boot Mode: HPI, 8-, 16-, and 32-Bit ROM Boot

Endianness: Little Endian, Big Endian

` 32-Bit External Memory Interface (EMIF)

Glueless Interface to SRAM, EPROM, Flash, SBSRAM, and SDRAM

512M-Byte Total Addressable External Memory Space

` Enhanced Direct-Memory-Access (EDMA) Controller (16 Independent Channels)

` 16-Bit Host-Port Interface (HPI)

` Two Multichannel Audio Serial Ports (McASPs)

Two Independent Clock Zones Each (1 TX and 1 RX)

Eight Serial Data Pins Per Port: Individually Assignable to any of the Clock Zones

Each Clock Zone Includes:

Programmable Clock Generator

Programmable Frame Sync Generator

TDM Streams From 2-32 Time Slots

Support for Slot Size: 8, 12, 16, 20, 24, 28, 32 Bits

Data Formatter for Bit Manipulation

Wide Variety of I2S and Similar Bit Stream Formats

Integrated Digital Audio Interface Transmitter (DIT) Supports:

S/PDIF, IEC60958-1, AES-3 Formats

Up to 16 transmit pins

Enhanced Channel Status/User Data RAM

Extensive Error Checking and Recovery

` Two Inter-Integrated Circuit (I2C) Buses Multi-Master and Slave Interfaces

` Two Multichannel Buffered Serial Ports (McBSPs):

Serial-Peripheral-Interface (SPI)

High-Speed TDM Interface

AC97 Interface

` Two 32-Bit General-Purpose Timers

` One Dedicated General-Purpose Input/Output Module With 16 pins

` Flexible Phase-Locked-Loop (PLL) Based Clock Generator Module

` IEEE-1149.1 (JTAG†) Boundary-Scan-Compatible

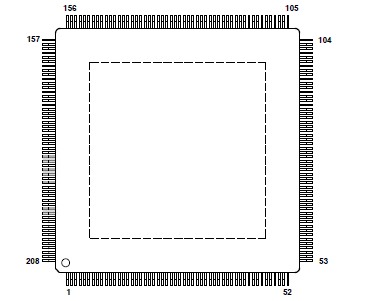

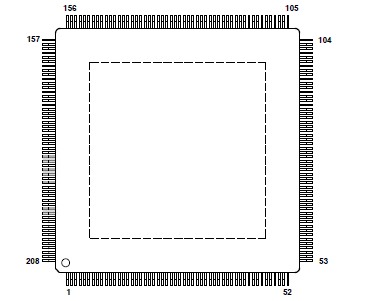

` Package Options:

208-Pin PowerPAD Plastic (Low-Profile) Quad Flatpack (PYP)

256-Pin Ball Grid Array Package (GFN)

` 0.13-m/6-Level Metal Process

CMOS Technology

` 3.3-V I/Os, 1.2-V Internal

Pinout Specifications

Specificationsabsolute maximum ratings over operating case temperature range (unless otherwise noted)†

Supply voltage range, CVDD (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to 1.35 V

Supply voltage range, DVDD (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to 4 V

Input voltage range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to DVDD + 0.5 V

Output voltage range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to DVDD + 0.5 V

Operating case temperature ranges, TC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 to 90

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 to 150

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to VSS.

DescriptionThe TMS320C67xTM DSPs (including the TMS320C6713 device) compose the floatingpoint DSP generation in the TMS320C6000TM DSP platform. The TMS320C6713 (C6713) TMS320C6713 is based on the high-performance, advanced VelociTITM very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making this DSP an excellent choice for multichannel and multifunction applications.

Operating at 225 MHz, the C6713 delivers up to 1350 million floating-point operations per second (MFLOPS), 1800 million instructions per second (MIPS), and with dual fixed-/floating-point multipliers up to 450 million multiply-accumulate operations per second (MMACS).

The TMS320C6713 uses a two-level cache-based architecture and has a powerful and diverse set of peripherals. The Level 1 program cache (L1P) is a 4K-Byte direct-mapped cache and the Level 1 data cache (L1D) is a 4K-Byte 2-way set-associative cache. The Level 2 memory/cache (L2) consists of a 256K-Byte memory space that is shared between program and data space. 64K Bytes of the 256K Bytes in L2 memory can be configured as mapped memory, cache, or combinations of the two. The remaining 192K Bytes in L2 serves as mapped SRAM.

The TMS320C6713 has a rich peripheral set that includes two Multichannel Audio Serial Ports (McASPs), two Multichannel Buffered Serial Ports (McBSPs), two Inter-Integrated Circuit (I2C) buses, one dedicated General-Purpose Input/Output (GPIO) module, two general-purpose timers, a host-port interface (HPI), and a glueless external memory interface (EMIF) capable of interfacing to SDRAM, SBSRAM, and asynchronous peripherals.

The two McASP interface modules each support one transmit and one receive clock zone. Each of the McASP has eight serial data pins which can be individually allocated to any of the two zones. The serial port supports time-division multiplexing on each pin from 2 to 32 time slots. The C6713 has sufficient bandwidth to support all 16 serial data pins transmitting a 192 kHz stereo signal. Serial data in each zone may be transmitted and received on multiple serial data pins simultaneously and formatted in a multitude of variations on the Philips Inter-IC Sound (I2S) format.

In addition, the McASP transmitter TMS320C6713 may be programmed to output multiple S/PDIF, IEC60958, AES-3 encoded data channels simultaneously, with a single RAM containing the full implementation of user data and channel status fields.

The McASP TMS320C6713 also provides extensive error-checking and recovery features, such as the bad clock detection circuit for each high-frequency master clock which verifies that the master clock is within a programmed frequency range.

The two I2C ports on the TMS320C6713 allow the DSP to easily control peripheral devices, boot from a serial EEPROM, and communicate with a host processor.

The TMS320C67x DSP generation is supported by the TI eXpressDSPTM set of industry benchmark development tools, including a highly optimizing C/C++ Compiler, the Code Composer StudioTM Integrated Development Environment (IDE), JTAG-based emulation and real-time debugging, and the DSP/BIOSTM kernel.

TMS320C6713 Data Sheet

TMS320C6713 Data Sheet