Features: *Powerful 16-Bit TMS320C5x CPU

*20-, 25-, 35-, and 50-ns Single-CycleInstruction Execution Time for 5-VOperation

*25-, 40-, and 50-ns Single-Cycle Instruction Execution Time for 3-V Operation

*Single-Cycle 16 ×16-Bit Multiply/Add

*224K × 16-Bit Maximum Addressable External Memory Space (64K Program, 64KData, 64K I/O, and 32K Global)

*2K, 4K, 8K, 16K, 32K ×16-Bit Single-AccessOn-Chip Program ROM

*1K, 3K, 6K, 9K × 16-Bit Single-AccessOn-Chip Program/Data RAM (SARAM)

*1K Dual-Access On-Chip Program/DataRAM (DARAM)

*Full-Duplex Synchronous Serial Port forCoder/Decoder Interface

*Time-Division-Multiplexed (TDM) Serial Port

*Hardware or Software Wait-StateGeneration Capability

*On-Chip Timer for Control Operations

*Repeat Instructions for Efficient Use ofProgram Space

*Buffered Serial Port

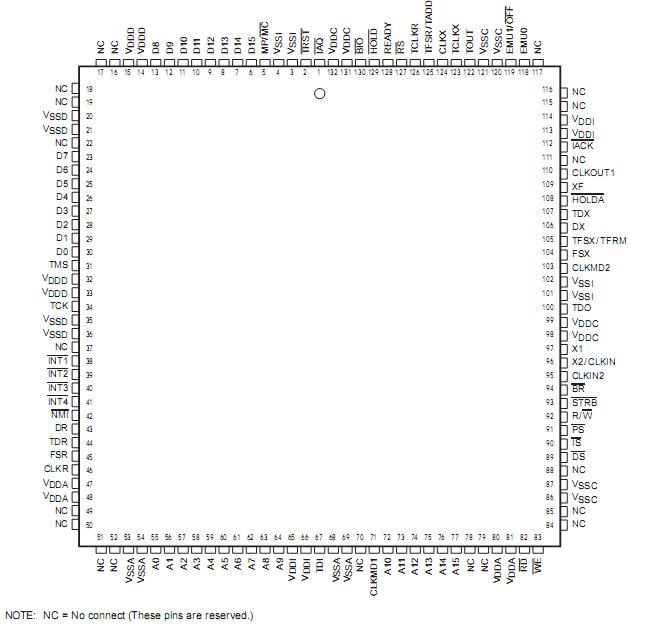

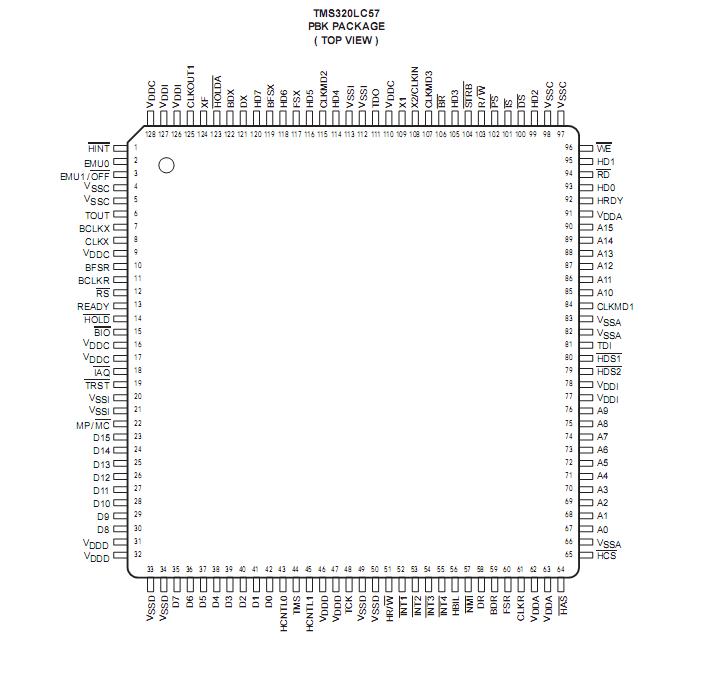

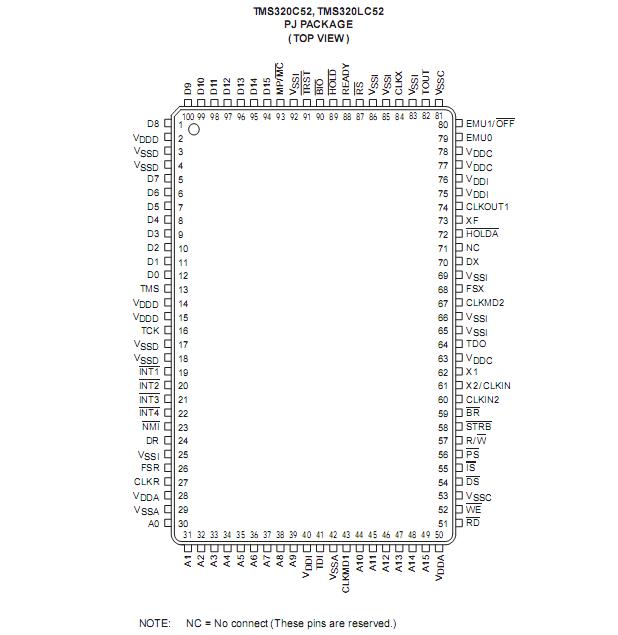

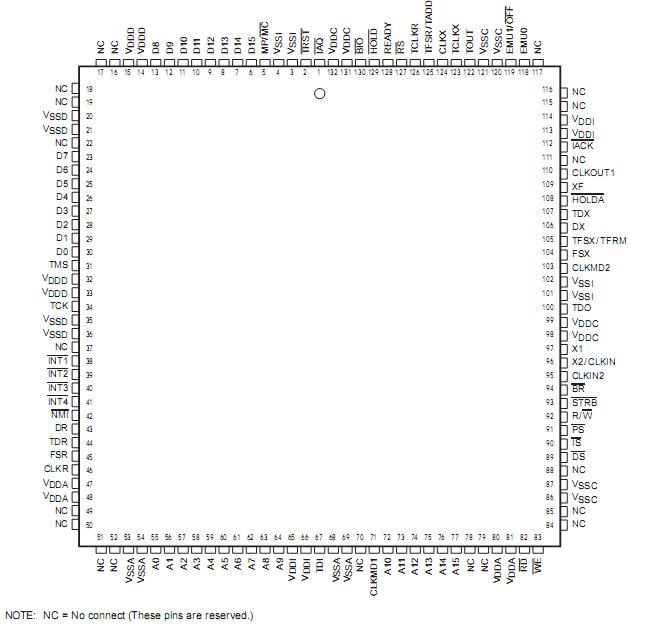

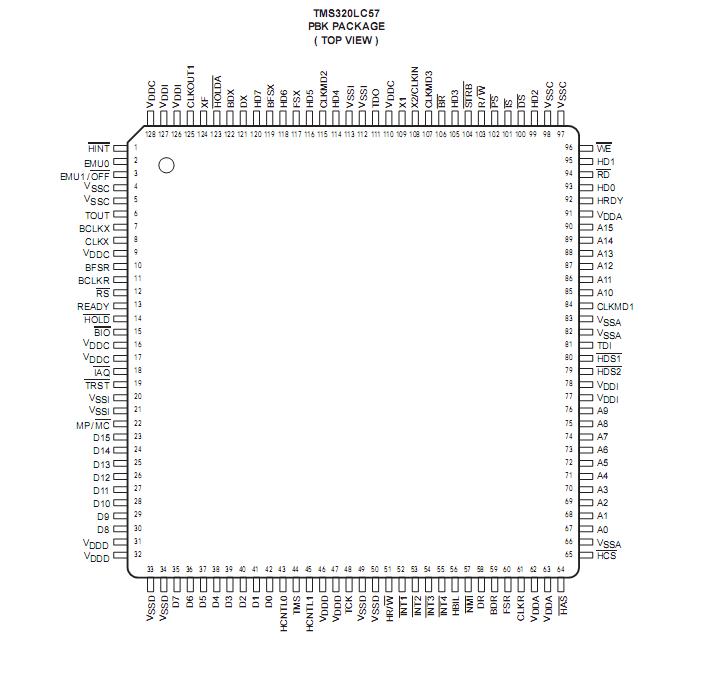

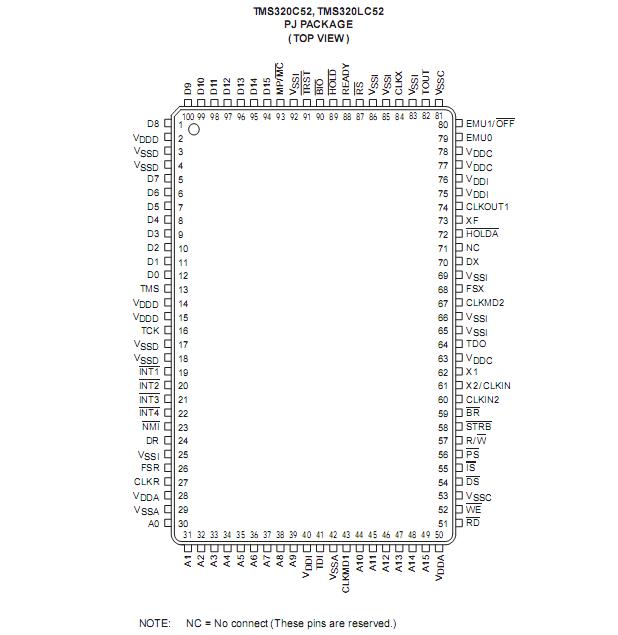

*Host Port InterfacePinout

Specifications

SpecificationsSupply voltage range, VDD

(see Note 3) 0.3 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to 7 V

Input voltage range, VI. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to 7 V

Output voltage range, VO ............................................................................................ 0.3 V to 7 V

Operating ambient temperature range, TA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40°C to 85°C

Operating case temperature, TC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to 85°C

Storage temperature range, T 55°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55°Cto 150

DescriptionThe TMS320C5x generation of the Texas Instruments (TI) TMS320 digital signal processors (DSPs) TMS320C5x isfabricated with static CMOS integrated circuit technology; the architectural design is based upon that of anearlier TI DSP, the TMS320C25. The combination of advanced Harvard architecture, on-chip peripherals,on-chip memory, and a highly specialized instruction set is the basis of the operational flexibility and speed ofthe 'C5x‡ devices. They execute up to 50 million instructions per second (MIPS).

The 'C5x TMS320C5x devices offer these advantages:

*Enhanced TMS320 architectural design for increased performance and versatility

*Modular architectural design for fast development of spin-off devices

*Advanced integrated-circuit processing technology for increased performance

*Upward-compatible source code (source code for 'C1x and 'C2x DSPs is upward compatible with 'C5x DSPs.)

*Enhanced TMS320 instruction set for faster algorithms and for optimized high-level language operation

*New static-design techniques for minimizing power consumption and maximizing radiation tolerance

TMS320C5x Data Sheet

TMS320C5x Data Sheet