Features: • Integrates eight E1 framers in a single device for terminating duplex E1 signals.

• Supports transfer of PCM data to/from 2.048 MHz system-side devices. Also supports a fractional E1 system interface with independent ingress/egress fractional E1 rates.

• Provides an optional backplane interface which is compatible with Mitel ST®- bus, AT&T CHI® and MVIP PCM backplanes, supporting data rates of 2.048 Mbit/s and 8.192 Mbit/s. Up to four links may be byte interleaved on each interface bus with no external circuitry.

• Extracts/inserts up to three HDLC links from/to arbitrary time slots to support the D-channel for ISDN Primary Rate Interfaces and the C-channels for V5.1/V5.2 interfaces as per ITU-T G.964, ITU-T G.965, ETS 300-324-1, and ETS 300-347-1.

• Provides jitter attenuation in the receive and transmit directions.

• Provides per-channel payload loopback and per link diagnostic and line loopbacks.

• Provides an integral pattern generator/detector that may be programmed to generate and detect common pseudo-random (as recommended in ITU-T O.151) or repetitive sequences. The programmed sequence may be inserted/detected in the entire E1 frame, or on a fractional E1 basis, in both the ingress and egress directions. Each framer possesses its own independent pattern generator/detector, and each detector counts pattern errors using a 32-bit saturating error counter.

• Provides signaling extraction and insertion on a per-channel basis.

• Software compatible with the PM6341 E1XC Single E1 Transceiver, the PM6344 EQUAD Quad E1 Framer, the PM4388 TOCTL Octal T1 Framer, and PM4351 COMET Combined E1/T1 Transceiver.

• Seamless interface to the PM4314 QDSX Quad Line Interface.

• Provides a IEEE P1149.1 (JTAG) compliant test access port (TAP) and controller for boundary scan test.

• Provides an 8-bit microprocessor bus interface for configuration, control, and status monitoring.

• Low power 3.3V CMOS technology with 5V tolerant inputs.

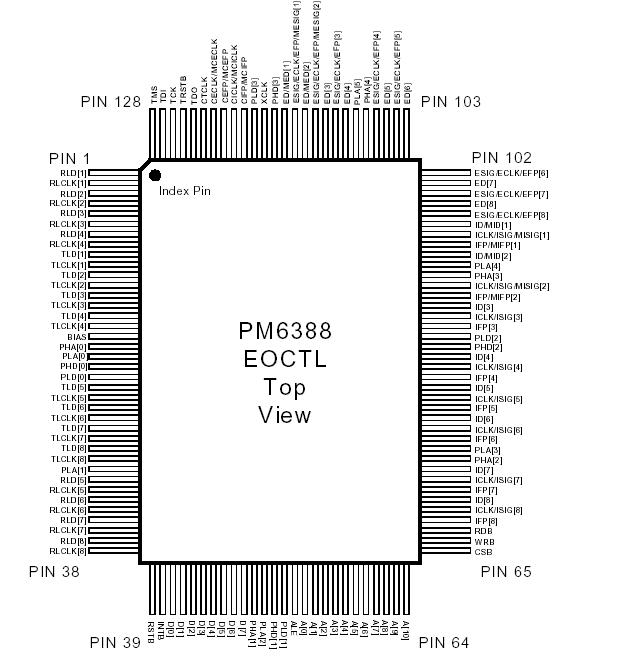

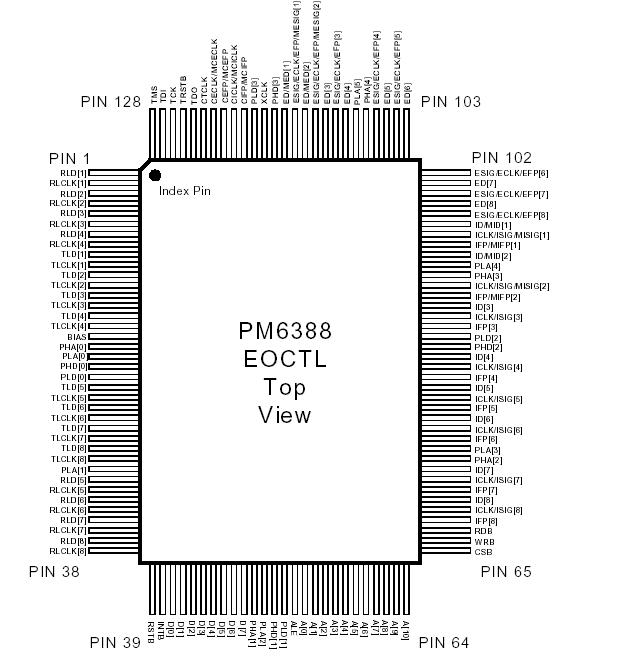

• Available in a 128 pin PQFP (14 mm by 20 mm) package.

• Provides a -40°C to +85°C Industrial temperature operating range.

Each one of eight receiver sections:

• Frames to ITU-T G.704 basic and CRC-4 multiframe formatted E1 signals. The framing procedures are consistent with ITU-T G.706 specifications.

• Red, and AIS alarm detection and integration are done according to ITU-T Q.431 specifications.

• Provides performance monitoring counters sufficiently large as to allow performance monitor counter polling at a minimum rate of once per second. Optionally, updates the performance monitoring counters and interrupts the microprocessor once per second, timed to the receive line. Accumulators are provided for counting CRC-4 errors, framing bit errors and loss of frame or change of frame alignment events.

• Provides an optional elastic store for backplane rate adaptation. It may be used to time the ingress streams to a common clock and frame alignment, or to facilitate per-channel loopbacks.

• Provides a digital phase locked loop to reduce jitter on the receive clock.

• Supports polled or interrupt-driven servicing of the HDLC interface.

• Optionally extracts a datalink in the E1 national use bits.

• Extracts up to three HDLC links from arbitrary time slots to support the Dchannel for ISDN Primary Rate Interfaces and the C-channels for V5.1/V5.2 interfaces.

• Frames to the E1 signaling multiframe alignment when enabled and extracts channel associated signaling. Alternatively, a common channel signaling data link may be extracted from timeslot 16.

• Can be programmed to generate an interrupt on change of signaling state.

• Provides trunk conditioning which forces programmable idle code substitution and signaling conditioning on all channels or on selected channels.

• Provides diagnostic, line loopbacks and per-channel line loopback.

• Provides programmable idle code substitution, data inversion, and A-Law or µ-Law digital milliwatt code insertion on a per-channel basis.

• Each one of eight transmitter sections:

• Transmits G.704 basic and CRC-4 multiframe formatted E1 signals.

• Supports unframed mode and framing bit, CRC, or data link by-pass.

• May be timed to its associated receive clock (loop timing) or may derive its timing from a common egress clock or a common transmit clock; the transmit line clock may be synthesized from an N*8kHz reference.

• Provides a 128 byte buffer to allow insertion of the facility data link using the host interface.

• Optionally inserts a datalink in the E1 national use bits.

• Inserts up to three HDLC links into arbitrary time slots to support the Dchannel for ISDN Primary Rate Interfaces and the C-channels for V5.1/V5.2 interfaces.

• Provides a digital phase locked loop for generation of a low jitter transmit clock.

• Provides programmable idle code substitution, data inversion, signaling insertion, and A-Law or µ-Law digital milliwatt code insertion on a per-channel basis.

Application• High density Internet E1 interfaces for multiplexers, switches, routers and digital modems.

• Frame Relay switches and access devices (FRADS)

• SONET/SDH Add Drop Multiplexers

• Digital Private Branch Exchanges (PBX)

• E1 Channel Service Units (CSU) and Data Service Units (DSU)

• E1 Channel Banks and Multiplexers

• Digital Access and Cross-Connect Systems (DACS)Pinout Specifications

Specifications

| Ambient Temperature under Bias |

-55°C to +125°C |

| Storage Temperature |

-65°C to +150°C |

| Voltage on VDD with Respect to GND |

-0.3V to 4.6V |

| Voltage on BIAS with respect to GND |

VDD - 0.3V to 5.5V |

| Voltage on Any Pin |

-0.3V to BIAS + 0.3V |

| Static Discharge Voltage |

±1000 V |

| Latchup current on any pin |

±100 mA |

| Maximum DC current on any pin |

±20 mA |

| Maximum Lead Temperature |

+230°C |

| Maximum Junction Temperature |

+150°C |

DescriptionThe PM6388 Octal E1 Framer (EOCTL) is a feature-rich device for use in systems carrying data (frame relay, Point to Point Protocol, or other protocols) or voice over E1 facilities. Each of the framers and transmitters is independently software configurable, allowing feature selection without changes to external wiring.

On the receive side, each of eight independent framers of PM6388 can be configured to frame to a basic G.704 2048 kbit/s signal as well as finding the signaling multiframe alignment signal and the CRC multiframe alignment:. Framing of PM6388 can also be bypassed (unframed mode). The EOCTL detects of PM6388 and indicates the presence various alarm conditions such as loss of frame-alignment, loss of signaling multiframe alignment, loss of CRC multiframe alignment, reception of remote alarm indication signals, remote multiframe alarm signals of PM6388 , alarm indication signal (AIS), and timeslot 16 alarm indication signal. The EOCTL integrates red and IS alarms as per industry specifications. Performance monitoring with accumulation of CRC-4 errors, far-end block errors, framing bit errors, and out-of-frame events is provided. The EOCTL also detects and terminates HDLC messages on TS16, the Sa National bits, and/or on any arbitrary timeslot. Each HDLC link is terminated in a 128 byte FIFO.

An elastic store of PM6388 that optionally supports slip buffering and adaptation to backplane timing of PM6388 is provided, as is a signaling extractor that supports signaling debounce, signaling freezing and interrupt on signaling state change on a per-channel basis. The EOCTL also supports idle code substitution and detection, digital milliwatt code insertion, data extraction, trunk conditioning, data inversion, and pattern generation or detection on a per-channel basis.

On the transmit side, the EOCTL generates framing of PM6388 for a G.704 2048 kbit/s E1 signal. Framing can be optionally disabled. The signaling multiframe alignment structure and the CRC multiframe structure may be optionally inserted. The EOCTL PM6388 supports signaling insertion, idle code substitution, data insertion, line loopback, data inversion, and test pattern generation or detection on a per-channel basis. Up to 3 HDLC links of PM6388 can be supported by the each octant of the EOCTL. Datalink messages can be transmitted on TS16, the Sa National bits, and on an arbitrary channel timeslot at the same time. The datalink messages may also be configured to operate on 3 arbitrary channel timeslots.

The EOCTL PM6388 can generate a low jitter transmit clock from a variety of clock references, and also provides jitter attenuation in the receive path.

The EOCTL PM6388 provides a parallel microprocessor interface for controlling the operation of the EOCTL device. Serial PCM interfaces allow 2048 kbit/s ingress/egress system interfaces to be directly supported.

The EOCTL PM6388 also supports an alternate backplane interface where up to 4 links can be byte-multiplexed onto one of two 8.192 Mbit/s buses. A link can be placed on either bus. Slots which are not occupied by a link from the EOCTL PM6388 device can be used by other devices attached to the bus. This bus protocol is consistent with that defined in the Mitel ST®, AT&T CHI® and MVIP PCM standards.

PM6388 should be noted that the EOCTL device operates on unipolar data only: HDB3 encoding and line code violation monitoring, if required, must be processed by the E1 LIU.

PM6388 Data Sheet

PM6388 Data Sheet