Features: • Complies with ANSI/TIA/EIA-644-A LVDS standard

• LVDS receiver inputs accept LVPECL signals

• Low jitter 660 Mbps fully differential data path

• Bus-Terminal ESD exceeds 2kV

• Single +3.3V supply voltage operation

• Receiver Differential Input Voltage Threshold < ±100mV

• Receiver open-circuit failsafe

• Low-Voltage Differential Signaling with typical Output Voltagesof 350mV into: 100 Load (PI90LV03) 50 Load (PI90LVB03)

• Typical Propagation Delay Times of 1.5ns

• Typical Power Dissipation of 20mW @ 200 MHz

• Outputs are High Impedance with VCC < 1.5V

• Industrial Temperature Range: 40°C to 85°C

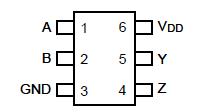

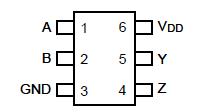

• Packaging:- 6-pin space-saving SOT-23 (T)ApplicationThe PI90LV03 and PI90LVB03 provide differential translationbetween LVDS and PECL devices for high-speed, point-to-pointinterface and telecom applications: ATM SONET/SDH Switches Routers Add-Drop MultiplexerPinout Specifications

SpecificationsSupply Voltage Range, VCC

(1) ...........................................................................0.5V to 4V

Voltage Range (A, B , or ROUT) .............................................. 0.5 to VCC +0.5V

ESD rating (HBIN, 1.5k, 100pF)............................................................................. 2V

Storage Temperature Range ..........................................................65°C to 150°C

Lead Temperature 1.6 mm (1/16 inch) from case for 10 seconds................ 250°C

Notes:

1. All voltage values, except differential I/O bus voltages, are with respect to ground terminal.

2. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, andfunctional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is notimplied. Exposure to Absolute-Maximum-Rated conditions for extended periods may affect device reliability.

Descriptionlow-voltage differential signaling (LVDS) to support data rates upto 660 Mbps. The PI90LVB03 features high-drive output. Bothproducts are designed for applications requiring high-speed, lowpowerconsumption, low-noise generation, and a small package.

The LVDS Repeaters take an LVDS input signal and provide anLVDS output to address various interface logic requirements suchas signal isolation, repeater, stub length, and Optical TransceiverModules. In many large systems, signals are distributed acrossbackplanes, and the distance between the transmission line and theunterminated receivers are one of the limiting factors for systemspeed. The buffers of PI90LVB03 can be used to reduce the 'stub length' by strategic PI90LVB03 placement along the trace length. PI90LVB03 can improvesystem performance by allowing the receiver to be placed veryclose to the main transmission line or very close to the connectoron the card. Longer traces to the LVDS receiver can then be placedafter the buffer.

The buffer's wide input dynamic range enables them to receive differentialsignals from LVPECL and LVDS sources. The PI90LVB03 can be used as compact high-speed serial translators between LVPECLand LVDS data lines. The differential translation provides a simpleway to mix and match Optical Transceiver ICs from various vendorswithout redesigning the interfaces.

PI90LV03 Data Sheet

PI90LV03 Data Sheet