Features: • Access Times: 15, 20, 25, 35, 45, 55 and 70 ns

• Battery Backup: 2V data retention

• Low power standby

• High-performance, low-power CMOS process

• Single +5V (±10%) Power Supply

• Easy memory expansion with CE\ and OE\ options.

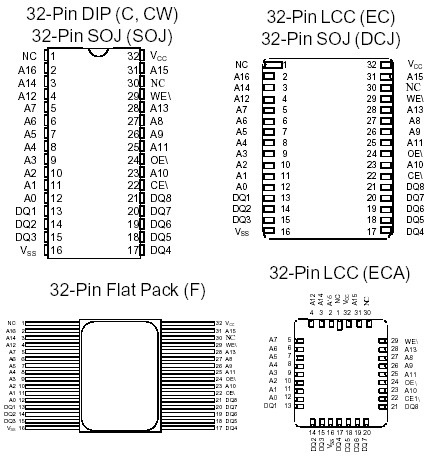

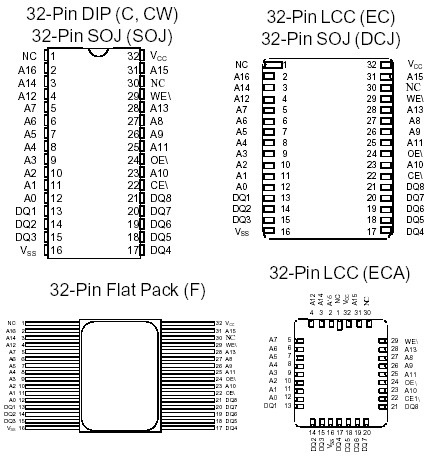

• All inputs and outputs are TTL compatiblePinout SpecificationsSupply Voltage Range (Vcc).............................-0.5V to +6.0V

SpecificationsSupply Voltage Range (Vcc).............................-0.5V to +6.0V

Storage Temperature......................................-65 to +150

Short Circuit Output Current (per I/O)........................20mA

Voltage on any Pin Relative to Vss..................-0.5V to +7.0V

Max Junction Temperature**.......................................+150

Power Dissipation ...............................................................1 WDescriptionThe MT5C1009 is a 1,048,576-bit high-speed CMOS static RAM organized as 131,072 words by 8 bits. This device uses 8 common input and output lines and has an output enable pin which operate faster than address access times during READ cycle.

For design flexibility in high-speed memory applications, this device offers chip enable (CE\) and output enable (OE\) features. These enhancements of MT5C1009 can place the outputs in High-Z for additional flexibility in system design. Writing to these devices is accomplished when write enable (WE\) and CE\ inputs are both LOW. Reading is accomplished when WE\ remains HIGH and CE\ and OE\ go LOW.

The MT5C1009 offer a reduced power standby mode when disabled, allowing system designs to achieve low standby power requirements.

The "L" version of MT5C1009 offers a 2V data retention mode, reducing current consumption to 2mW maximum.

MT5C1009 operate from a single +5V power supply and all inputs and outputs are fully TTL compatible. It is particularly well suited for use in high-density, high-speed system applications.

MT5C1009 Data Sheet

MT5C1009 Data Sheet