Features: • MCM69F618C8.5 = 8.5 ns Access / 12 ns Cycle

MCM69F618C9 = 9 ns Access / 12 ns Cycle

MCM69F618C10 = 10 ns Access / 15 ns Cycle

MCM69F618C12= 12 ns Access / 16.6 ns Cycle

• Single 3.3 V + 10%, 5% Power Supply

• ADSP, ADSC, and ADV Burst Control Pins

• Selectable Burst Sequencing Order (Linear/Interleaved)

• Internally SelfTimed Write Cycle

• Byte Write and Global Write Control

• 5 V Tolerant on all Pins (Inputs and I/Os)

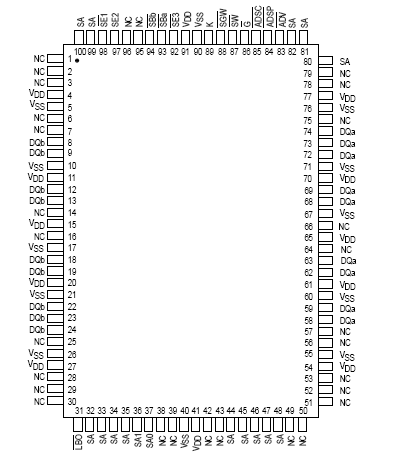

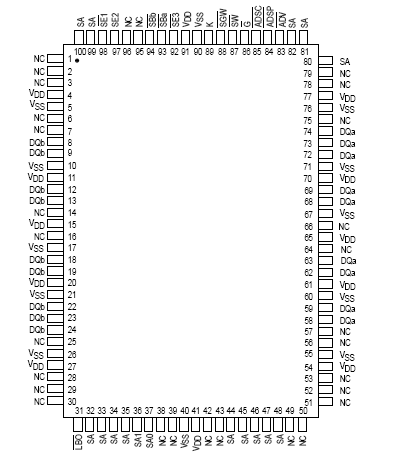

• 100Pin TQFP PackagePinout Specifications

Specifications

| Rating |

Symbol |

Value |

Unit |

| Power Supply Voltage |

VDD |

0.5 to + 4.6 |

V |

Voltage Relative to VSS for Any

Pin Except VDD |

Vin, Vout |

0.5 to 6.0 |

V |

| Output Current (per I/O) |

Iout |

± 20 |

mA |

| Package Power Dissipation (See Note 2) |

PD |

1.6 |

W |

| Temperature Under Bias |

Tbias |

10 to 85 |

°C |

| Storage Temperature |

Tstg |

55 to 125 |

°C |

DescriptionThe MCM69P618C is a 1Mbit synchronous fast static RAM designed to provide a burstable, high performance, secondary cache for the 68K Family, PowerPCE, 486, i960™, and Pentium™ microprocessors. It is organized as 64K words of 18 bits each. This device integrates input registers, a 2bit address counter, and high speed SRAM onto a single monolithic circuit for reduced parts count in cache data RAM applications. Synchronous design allows precise cycle control with the use of an external clock (K). BiCMOS circuitry reduces the overall power consumption of the integrated functions for greater reliability.

Addresses (SA), data inputs (DQx) of the MCM69P618C, and all control signals except output enable (G) and Linear Burst Order (LBO) are clock (K) controlled through positiveedgetriggered noninverting registers.

Bursts of the MCM69P618C can be initiated with either ADSP or ADSC input pins. Subsequent burst addresses can be generated internally by the MCM69F618C (burst sequence operates in linear or interleaved mode dependent upon the state of LBO) and controlled by the burst address advance (ADV) input pin.

Write cycles of the MCM69P618C are internally selftimed and initiated by the rising edge of the clock (K) input. This feature eliminates complex offchip write pulse generation and provides increased timing flexibility for incoming signals.

Synchronous byte write (SBx), synchronous global write (SGW), and synchronouswrite enable SW are provided to allow writes to either individual bytes or to both bytes. The two bytes are designated as "a" and "b". SBa controls DQa and SBb controls DQb. Individual bytes are written if the selected byte writes SBx are asserted with SW. Both bytes are written if either SGW of the MCM69P618C is asserted or if all SBx and SW are asserted.

For read cycles, a flowthrough SRAM allows output data to simply flow freely from the memory array.

The MCM69P618Coperates from a 3.3 V power supply and all inputs and outputs are LVTTL compatible and 5 V tolerant.

MCM69P618C Data Sheet

MCM69P618C Data Sheet