Features: • Single 5 V ± 5% Power Supply

• Fast Access Time/Fast Cycle Time = 6 ns/100 MHz, 7 ns/80 MHz, 9 ns/66 MHz

• Byte Writeable via Dual Write Enables

• Internal Input Registers (Address, Data, Control)

• Output Registers for Pipelined Applications

• Internally SelfTimed Write Cycle

• ADSP, ADSC, and ADV Burst Control Pins

• Asynchronous Output Enable Controlled ThreeState Outputs

• Common Data Inputs and Data Outputs

• 3.3 V I/O Compatible

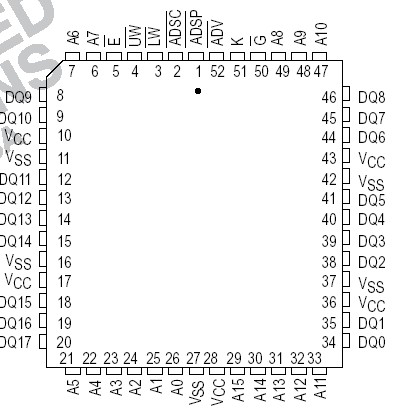

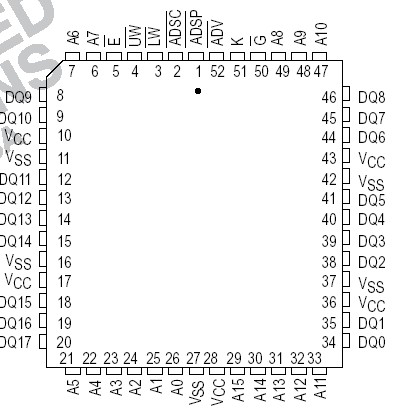

• High Board Density 52Lead PLCC Package

Pinout Specifications

Specifications

|

Rating |

Symbol |

Value |

Unit |

| Power Supply Voltage |

VCC |

0.5 to + 7.0 |

V |

Voltage Relative to VSS for Any

Pin Except VCC |

Vin, Vout |

0.5 to VCC + 0.5 |

V |

| Output Current (per I/O) |

Iout |

± 30 |

mA |

| Power Dissipation |

PD |

16 |

W |

| Temperature Under Bias |

Tbias |

10 to + 85 |

°C |

| Operating Temperature |

TA |

0 to +70 |

°C |

| Storage Temperature |

Tstg |

55 to + 125 |

°C |

DescriptionThe MCM67C618 is a 1,179,648 bit synchronous static random access memory designed to provide a burstable, highperformance, secondary cache for the i486E and PentiumE microprocessors. It is organized as 65,536 words of 18 bits, fabricated with Motorola's highperformance silicongate BiCMOS technology. The device integrates input registers, a 2bit counter, high speed SRAM, and high drive registered output drivers onto a single monolithic circuit for reduced parts count implementation of cache data RAM applications. Synchronous design allows precise cycle control with the use of an external clock (K). BiCMOS circuitry reduces the overall power consumption of the integrated functions for greater reliability.

Addresses (A0 A15), data inputs (D0 D17), and all control signals except output enable (G) are clock (K) controlled through positiveedgetriggered noninverting registers.

This device contains output registers for pipeline operations. At the rising edge of K, the RAM provides the output data from the previous cycle.

Output enable (G) is asynchronous for maximum system design flexibility.

Burst can be initiated with either address status processor (ADSP) or address status cache controller (ADSC) input pins. Subsequent burst addresses can be generated internally by the MCM67C618 (burst sequence imitates that of the i486) and controlled by the burst address advance (ADV) input pin. The following pages provide more detailed information on burst controls.

Write cycles are internally selftimed and are initiated by the rising edge of the clock (K) input. This feature eliminates complex offchip write pulse generation and provides increased flexibility for incoming signals.

Dual write enables (LW and UW) are provided to allow individually writeable bytes. LW controls DQ0 DQ8 (the lower bits), while UW controls DQ9 DQ17 (the upper bits).

This device is ideally suited for systems that require wide data bus widths and cache memory. See Figure 2 for applications information.

MCM67C618 Data Sheet

MCM67C618 Data Sheet