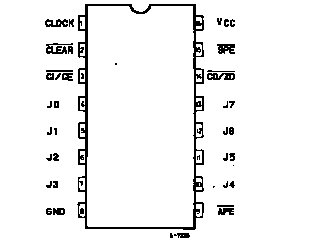

M74HC40103: Features: ` HIGH SPEED : fMAX = 38MHz (TYP.) at VCC = 6V` LOW POWER DISSIPATION: ICC =4A(MAX.) at TA=25` HIGH NOISE IMMUNITY: VNIH = VNIL = 28 % VCC (MIN.)` SYMMETRICAL OUTPUT IMPEDANCE: |IOH| = IOL...

floor Price/Ceiling Price

- Part Number:

- M74HC40103

- Supply Ability:

- 5000

Price Break

- Qty

- 1~5000

- Unit Price

- Negotiable

- Processing time

- 15 Days

SeekIC Buyer Protection PLUS - newly updated for 2013!

- Escrow Protection.

- Guaranteed refunds.

- Secure payments.

- Learn more >>

Month Sales

268 Transactions

Payment Methods

All payment methods are secure and covered by SeekIC Buyer Protection PLUS.

M74HC40103 Data Sheet

M74HC40103 Data Sheet