Features: ·HIGH SPEED

tPD = 13 ns (TYP.) AT VCC = 5 V

· LOWPOWER DISSIPATION

ICC = 4 mA (MAX.) at TA = 25 °C

·HIGH NOISE IMMUNITY

VNIH = VNIL = 28 % VCC (MIN.)

·OUTPUT DRIVE CAPABILITY

10 LSTTL LOADS

·SYMMETRICAL OUTPUT IMPEDANCE

|IOH| = IOL = 4 mA (MIN.)

·BALANCEDPROPAGATION DELAYS

tPLH = tPHL

· WIDE OPERATING VOLTAGE RANGE

VCC (OPR) = 2 V to 6 V

·PIN AND FUNCTION COMPATIBLE WITH 54/74LS181Pinout Specifications

Specifications

| Symbol |

Parameter |

Value |

Unit |

| VCC |

Supply Voltage |

-0.5 to +7 |

V |

| VI |

DC Input Voltage |

-0.5 to VCC + 0.5 |

V |

| VO |

DC Output Voltage |

-0.5 to VCC + 0.5 |

V |

| IIK |

DC Input Diode Current |

± 20 |

mA |

| IOK |

DC Output Diode Current |

± 20 |

mA |

| IO |

DC Output Current |

± 25 |

mA |

| ICC or IGND |

DC VCC or Ground Current |

± 50 |

mA |

| PD |

Power Dissipation |

500(*) |

mW |

| Tstg |

Storage Temperature |

-65 to +150 |

°C |

| TL |

Lead Temperature (10 sec) |

300 |

°C |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operationunder these conditions is not implied

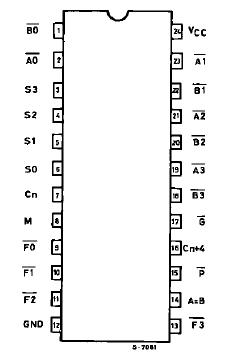

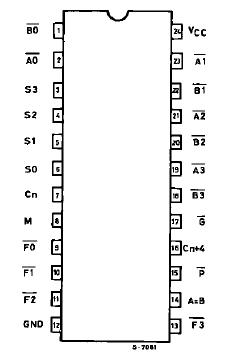

(*) 500mW at 65 °C; derate to 300mW by 10mW/°C from 65°C to 85°C DescriptionThe 74HC181 is a high speed CMOS ARITHMETIC LOGIC UNIT/FUNCTION GENERATOR fabricated with silicon gate C2MOS technology. It has the same highspeed performance ofLSTTL combined withtrue CMOS low power consumption. These circuits perform 16 binary arithmetic operations on two 4-bit words as shown in tables 1 and 2. These operations are selected by the four function-select lines (S0, S1, S2, S3) andinclude addition, subtraction, decrement, and straight transfer. When performing arithmetic manipulations, theinternal carriesmust be enabled by applying a low-level voltage to themode control input (M). Afull carry look-ahead scheme ismade available in these devices for fast, simultaneous carry generation by means of two cascade-outputs (pins 15 and 17) for thefour bits in the package. Whenused in conjunction with theM54HC182 or M74HC182, full carry look-ahead circuits, high-speed arithmetic operations can be performed.

These circuits 74HC181 will accomodate active- high oractive-low data, if the pin designations are interpreted as shown below. Subtraction is accomplished by 1,s complement addition where the 1's complement of thesubtrahend is generated internally. The resultant output is 1B1, which requires an endaround or forced carry to produce AB. The 181 can also be utilized as a comparator. The A = B output is internally decoded from the function outputs (F0, F1, F2, F3) so that when two words of equal magnitude are applied at the Aand Binputs, itwill assume a high level to indicated equality (A = B). The ALUshould be in thesubtractmode withCn =Hwhen performing this comparison. The A = B output is open-drain so that it can be wire-AND connected to give a comparison for more that four bits. The carry output (Cn + 4) can also be used to supply relative magnitude information. Again, theALUshould be placed in the subtract mode by placing the function select inputs S3, S2, S1, S0 at L, H, H, L, respectively.

These circuits 74HC181 have been designed to not only incorporate all of the designer's requirements for arithmetic operations, but also to provide 16 possible functions of two Boolean variables without the use of external circuitry. These logic functions are selected by use of the four function-select inputs (S0, S1, S2, S3) with the mode-control input (M) at a high level to disable the internal carry. All inputs are equipped withprotection circuitsagainst static discharge and transient excess voltage.

M74HC181 Data Sheet

M74HC181 Data Sheet