Pinout Specifications

Specifications| Function | Transmitter |

| Bits | 18 or 24 |

| Max PCLK Frequency | 30 MHz |

| VDDP | 1.6V to 2.0V |

| VDDI/O | 1.6V to 2.0V |

| Target Application | Mobile Phone |

| Recommended Interface | RGB |

| Selectable Edge Rate | Yes |

| PowerWise Technology | Mobile Pixel Link Bridge |

| External Filters Req'd | No |

| I/O Levels | MPL-2 |

| Special Features | Auto Power Down on Stop Clock , SPI Interfac |

| ESD | 2 kV |

| View Using Catalog |

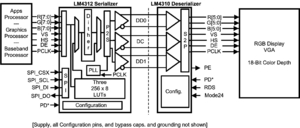

DescriptionThe LM4312 is a MPL-2 Serializer (SER) that accepts a 24- or 18-RGB interface and serializes this wide bus to 3 differential signals. The optional Dithering feature can reduce 24-bit RGB to 18-bit RGB. The optional Look Up Table (Three X 256 X 8 bit RAM) is provided for independent color correction. 18-bit Bufferless displays from QVGA (320 x 240) up to >VGA (640 x 480) pixels are supported.

The interconnect is reduced from 28 LVCMOS signals (RGB888+V+H+DE+PCLK) to only 3 active differential signals (DD0P/M, DCP/M, DD1P/M) with the LM4312 Serializer and companion LM4310 Deserializer easing flex interconnect design, size constraints and cost.

The LM4312 SER resides by the application, graphics or baseband processor and translates the wide parallel video bus from LVCMOS levels to serial MPL-2 levels for transmission over a flex cable and PCB traces to the DES located in the display module.

When in Power_Down, the SER is put to sleep and draws less than 10A. The SER can be powered down by stopping the PCLK or by asserting its PD* input pin.

The LM4312 implements the physical layer of the MPL-2 Interface and features robust common-mode noise rejection.

LM4312 Data Sheet

LM4312 Data Sheet