Features: ` Pin-Compatible and Functionally Upwards-Compatible with Sharp LH5420 and LH543601, but Deeper

` Expanded Control Register that is Fully Readable as well as Writeable

` Fast Cycle Times: 18/20/25/30/35 ns

` Improved Input Setup and Flag Out Timing

` Two 512*36-bit FIFO Buffers (LH543611) or Two 1024*36-bit FIFO Buffers (LH543621)

` Full 36-bit Word Width

` Selectable 36/18/9-bit Word Width on Port B; Selection May be Changed Without Resetting the BiFIFO

` Programmable Byte-Order Reversal 'Big-Endian  Little-Endian Conversion'

Little-Endian Conversion'

` Independently-Synchronized ('Fully-Asynchronous') Operation of Port A and Port B

` 'Synchronous' Enable-Plus-Clock Control at Both Ports

` R/W, Enable, Request, and Address Control Inputs are Sampled on the Rising Clock Edge

` Synchronous Request/Acknowledge 'Handshake' Capability; Use is Optional

` Device Comes Up Into a Known Default State at Reset; Programming is Allowed, but is not Required

` Asynchronous Output Enables

` Five Status Flags per Port: Full, Almost-Full, Half-Full, Almost-Empty, and Empty

` All Flags are Independently Programmable for Either Synchronous or Asynchronous Operation

` Almost-Full Flag and Almost-Empty Flag Have Programmable Offsets

` Mailbox Registers with Synchronized Flags

` Data-Bypass Function

` Data-Retransmit Function

` Automatic Byte Parity Checking with Programmable Parity Flag Latch

` Programmable Byte Parity Generation

` Programmable Byte, Half-Word, or Full-Word Oriented Parity Operations

` 8 mA-IOL High-Drive Three-State Outputs with Built-In Series Resistor

` TTL/CMOS-Compatible I/O

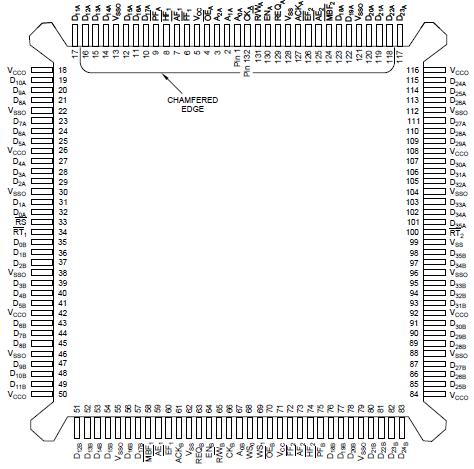

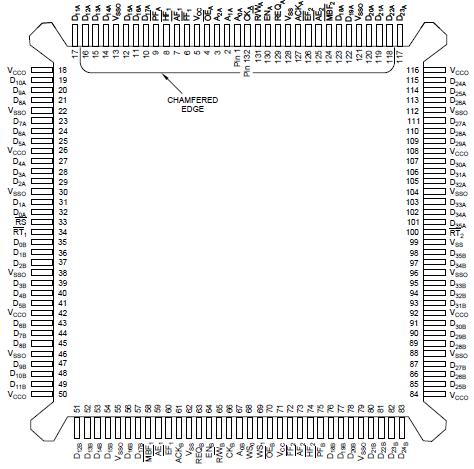

` Space-Saving PQFP and TQFP PackagesPinout Specifications

Specifications

| Parameter |

RATING |

| Supply Voltage to VSS Potential |

0.5 V to 7 V |

| Signal Pin Voltage to VSS Potential 3 |

0.5 V to VCC + 0.5 V |

| DC Output Current 2 |

± 40 mA |

| Storage Temperature Range |

65 to 150 |

| Power Dissipation (Package Limit) |

2 Watts (Quad Flat Pack) |

NOTES:

1. Stresses greater than those listed under 'Absolute Maximum Ratings' may cause permanent damage to the device. This is a stress rating for transient conditions only. Functional operation of the device at these or any other conditions outside those indicated in the 'Operating Range' of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Outputs should not be shorted for more than 30 seconds. No more than one output should be shorted at any time.

3. Negative undershoot of 1.5 V in amplitude is permitted for up to 10 ns, once per cycle. DescriptionThe LH543611 and LH543621 contain two FIFO buffers, FIFO #1 and FIFO #2. These operate in parallel, but in opposite directions, for bidirectional data buffering. FIFO #1 and FIFO #2 each are organized as 512 or 1024 by 36 bits. The LH543611 and LH543621 are ideal either for wide unidirectional applications or for bidirectional data applications; component count and board area are reduced.

The LH543611 and LH543621 have two 36-bit ports, Port A and Port B. Each port has its own port-synchronous clock, but the two ports may operate asynchronously relative to each other. Data flow is initiated at a port by the rising edge of the appropriate clock; it is gated by the corresponding edge-sampled enable, request, and read/write control signals. At the maximum operating frequency, the clock duty cycle may vary from 40% to 60%. At lower frequencies, the clock waveform may be quite asymmetric, as long as the minimum pulse-width conditions for clock-HIGH and clock-LOW remain satisfied; the LH543611 and LH543621 are fully-static parts.

Conceptually, the port clocks CKA and CKB are freerunning, periodic 'clock' waveforms, used to control other signals which are edge-sensitive. However, there actually is not any absolute requirement that these 'clock' waveforms must be periodic. An 'asynchronous' mode of operation is possible, in one or both directions, independently, if the appropriate enable and request inputs are continuously asserted, and enough aperiodic 'clock' pulses of suitable duration are generated by external logic to cause all necessary actions to occur.

A synchronous request/acknowledge handshake facility is provided at each port for FIFO data access. This request/ acknowledge handshake resolves FIFO full and empty boundary conditions, when the two ports are operated asynchronously relative to each other.

FIFO status flags monitor the extent to which each FIFO buffer has been filled. Full, Almost-Full, Half-Full, Almost-Empty, and Empty flags are included for each FIFO. Each of these flags may be independently programmed for either synchronous or asynchronous operation. Also, the Almost-Full and Almost-Empty flags are programmable over the entire FIFO depth, but are automatically initialized to eight locations from the respective FIFO boundaries at reset. A data block of 512 (LH543611) or 1024 (LH543621) or fewer words may be retransmitted any desired number of times.

LH543621 Data Sheet

LH543621 Data Sheet

Little-Endian Conversion'

Little-Endian Conversion'