Features: • 131072 words × 16 bits configuration.

• Single 5 V ± 10% power supply.

• All input and output (I/O) TTL compatible.

• Supports fast page mode, read-modify-write and byte write.

• Supports output buffer control using early write and Output Enable (OE) control.

• 8 ms refresh using 512 refresh cycles.

• Supports RAS-only refresh, CAS-before-RAS refresh and hidden refresh.

• Follows the JEDEC 1 M DRAM (65536 words × 16 bits, 1CAS/2WE) standard.

• RAS access time/column address time/CAS access time/cycle time/power dissipation

• Package:

SOJ 40-pin (400 mil) plastic package : LC322271J

SOP 40-pin (450 mil) plastic package: LC322271M

TSOP 44-pin (400 mil) plastic package : LC322271T

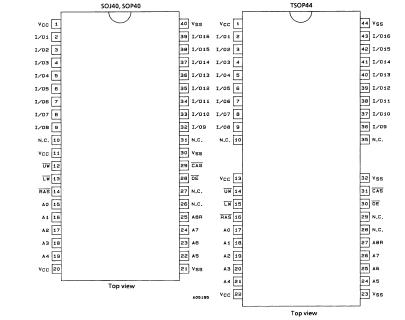

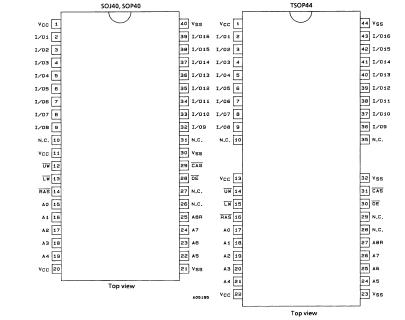

Pinout Specifications

Specifications

|

Characteristic |

Symbol |

Ratings |

Unit |

Note |

| Maximum supply voltage |

VCCmax |

1.0 to +7.0 |

V |

1 |

| Input voltage |

VIN |

1.0 to +7.0 |

V |

1 |

| Output voltage |

VOUT |

1.0 to +7.0 |

V |

1 |

| Allowable power dissipation |

LC322271J, M |

PDmax |

800 |

mW |

1 |

| LC322271T |

700 |

| Output short-circuit current |

IOUT |

50 |

mA |

1 |

| Operating Temperature range |

TOPR |

0 to +70 |

°C |

1 |

| Storage temperature range |

TSTG |

55 to +150 |

°C |

1 |

Note: 1. Stresses greater than the above listed maximum values may result in damage to the device.

DescriptionThe LC322271J, M and T is a CMOS dynamic RAM operating on a single 5 V power source and having a 131072 words ´ 16 bits configuration. Equipped with large capacity capabilities, high speed transfer rates and low power dissipation, this series is suited for a wide variety of applications ranging from computer main memory and expansion memory to commercial equipment.

Address input utilizes a multiplexed address bus which permits it to be enclosed in a compact plastic package of SOJ 40-pin, SOP 40-pin, and TSOP 44-pin . Refresh rates are within 8 ms with 512 row address (A0 to A7, A8R) selection and support Row Address Strobe (RAS)-only refresh, Column Address Strobe (CAS)-before-RAS refresh and hidden refresh settings. There are functions such as fast page mode, read-modify-write and byte write. The pin assignment follows the JEDEC 1 M DRAM (65536 words × 16 bits, 1CAS/2WE) standard.

LC322271J Data Sheet

LC322271J Data Sheet