Features: • Block Oriented 24-Bit Sequencer

• Configurable as Two Independent 12-Bit Sequencers

• 24 x 24 Crosspoint Switch

• Programmable Delay on 12 Outputs

• Multi-Chip Synchronization Signals

• Standard P Interface

• 100pF Drive on Outputs

• DC to 50MHz Clock RateApplication• 1-D, 2-D Filtering

• Pan/Zoom Addressing

• FFT Processing

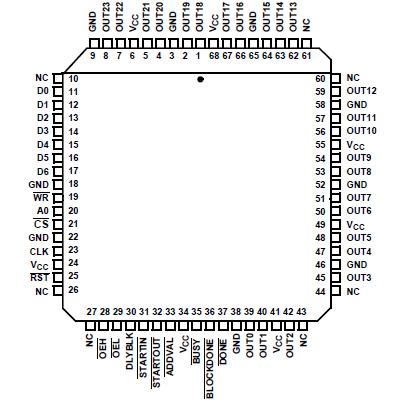

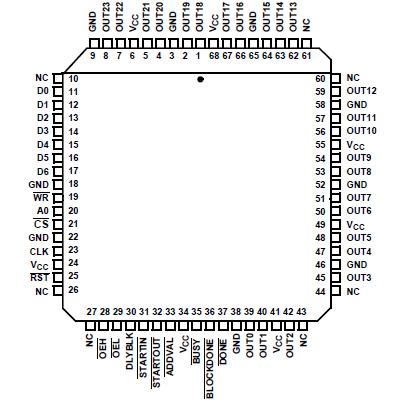

• Matrix Math OperationsPinout Specifications

SpecificationsSupply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+6.0V

Input, Output or I/O Voltage Applied. . . . . GND -0.5V to VCC +0.5V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

DescriptionThe Intersil HSP45240 is a high speed Address Sequencer which provides specialized addressing for functions like FFTs, 1-D and 2-D filtering, matrix operations, and image manipulation. The sequencer supports block oriented addressing of large data sets up to 24-bits at clock speeds up to 50MHz.

Specialized addressing requirements are met by using the onboard 24 x 24 crosspoint switch. This HSP45240 feature allows the mapping of the 24 address bits at the output of the address generator to the 24 address outputs of the chip. As a result, bit reverse addressing, such as that used in FFTs, is made possible.

A single chip solution to read/write addressing is also made possible by configuring the HSP45240 as two 12-bit sequencers. To compensate for system pipeline delay, a programmable delay is provided on 12 of the address outputs.

The HSP45240 is manufactured using an advanced CMOS process, and is a low power fully static design. The configuration of the device is controlled through a standard microprocessor interface and all inputs/outputs, with the exception of clock, are TTL compatible.

HSP45240 Data Sheet

HSP45240 Data Sheet