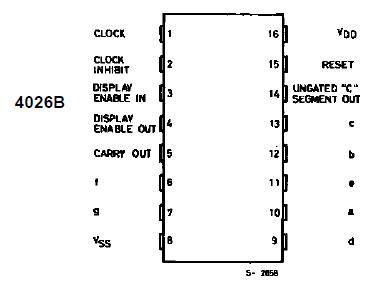

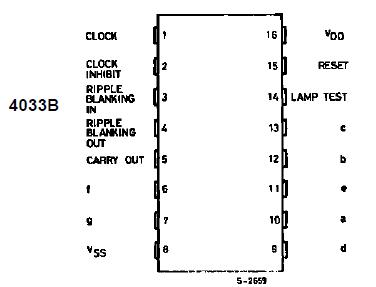

Pinout

Specifications

Specifications

| Symbol |

Parameter |

Value |

Unit |

| VDD* |

Supply Voltage : HCC Types

HCF Types |

0.5 to + 20

0.5 to + 18 |

V

V |

| Vi |

Input Voltage |

0.5 to VDD + 0.5 |

V |

| II |

DC Input Current (any one input) |

± 10 |

mA |

| Ptot |

Total Power Dissipation (per package)

Dissipation per Output Transistor

for Top = Full Package-temperature Range |

200

100 |

mW

mW |

| Top |

Operating Temperature : HCC Types

HCF Types |

55 to + 125

40 to + 85 |

°C

°C |

| Tstg |

Storasge Temperature |

65 to + 150 |

°C |

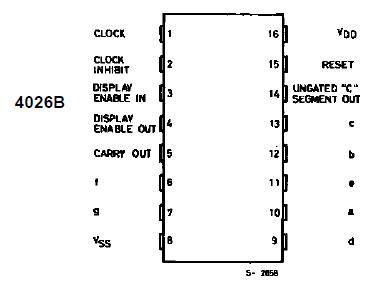

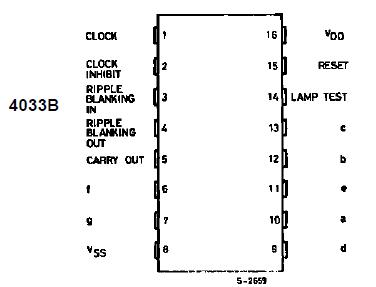

DescriptionIn the HCC/HCF4026B, HCC/HCF4033B series, the HCC4026B/4033B (extended temperature range) and HCF4026B/4033B (intermediate temperature range) are monolithic integrated circuits, available in 16-lead dual in-line plastic or ceramic package and plastic micro package. The HCC/HCF4026B and HCC/HCF4033B each consist of a 5-stage Johnson decade counter and an output decoder which converts the Johnson code to a 7-segment decoded output for driving one stage in a numerical display. These devices are particularly advantageous in display applications where low power dissipation and/or low package count are important. Inputs common to both types are CLOCK, RESET, & CLOCK INHIBIT ; common outputs are CARRY OUT and the seven decoded outputs (a, b, c, d, e, f, g). Additional inputs and outputs for the HCC/HCF4026B include DISPLAY ENABLE input and DISPLAY ENABLE and UNGATED "CSEGMENT" outputs. Signals peculiar to the HCC/HCF4033B are RIPPLE-BLANKING INPUT AND LAMP TEST INPUT and a RIPPLE-BLANKING OUTPUT. A high RESET signal clears the de-cade counter to its zero count. The counter is advanced one count at the positive clock signal transition if the CLOCK INHIBIT signal is low. Counter advancement via the clock line is inhibited when the CLOCK INHIBIT signal is high. Antilock gating is provided on the JOHNSON counter, thus assuring proper counting sequence. The CARRY-OUT (Cout) signal completes one cycle every ten CLOCK INPUT cycles and is used to clock the succeeding decade directly in a multi-decade counting chain. The seven decoded outputs (a, b, c, d, e, f, g) illuminate the proper segments in a seven segment display device used for representing the decimal numbers 0 to 9. The 7-segment outputs go high on selection in the HCC/HCF4026B, HCC/HCF4033B outputs go high only when the DISPLAY ENABLE IN is high.

HCC/HCF4026B, HCC/HCF4033B -When the DISPLAY ENABLE IN is low the seven decoded outputs are forced low regardless of the state of the counter. Activation of the display only when required results in significant power savings. This system also facilitates implementation of display-character multiplexing. The CARRY OUT and UNGATED "C-SEGMENT" signals are not gated by the DISPLAY ENABLE and therefore are available continuously. This feature is a requirement in implementation of certain divider functions such as divide-by-60 and divide-by-12.

HCC/HCF4026B, HCC/HCF4033B have provisions for automatic blanking of the non-significant zeros in a multi-digit decimal number which results in an easily readable display consistent with normal writing practice. For example, the number 0050.07000 in an eight digit display would be displayed as 50.07. Zero suppression on the integer side is obtained by connecting the RBI terminal of the HCC/HCF4033B associated with the most significant digit in the display to a low-level voltage and connecting the RBOterminal of that stageto the RBI terminal of the HCC/HCF4033B in the next-lower significant position in the display. This procedure is continued for each succeeding HCC/HCF4033B on the integer side of the display. On the fraction side of the display the RBI of the HCC/HCF4033B associated with the least significant bit is connected to a low-level voltage and the RBO of that HCC/- HCF4033B is connected to the RBI terminal of the HCC/HCF4033B in the next more-significant-bit position. Again, this procedure is continued for all HCC/HCF4033B's on the fraction side of the display. In a purely fractional number the zero immediately preceding the decimal point can be displayed by connecting the RBI of that stage to a high level voltage (instead of to the RBO of the next more-significant- stage). For example : optional zero " 0.7346. Likewise, the zero in a number such as 763.0 can be displayed by connecting the RBI of the HCC/HCF4033B associated with it to a high-level voltage. Ripple blanking of non-significant zeros provides an appreciable savings in display power. The HCC/HCF4026B, HCC/HCF4033B have a LAMP TEST input which, when connected to a high-level voltage, overrides normal decoder operation and enables a check to be made on possible display malfunctions by putting the seven outputs in the high state.

HCF4033B Data Sheet

HCF4033B Data Sheet