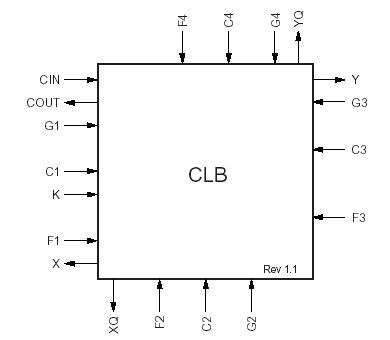

DS060: Features: First ASIC replacement FPGA for high-volume production with on-chip RAMDensity up to 1862 logic cells or 40,000 system gatesStreamlined feature set based on XC4000 architectureSystem perfo...

floor Price/Ceiling Price

- Part Number:

- DS060

- Supply Ability:

- 5000

Price Break

- Qty

- 1~5000

- Unit Price

- Negotiable

- Processing time

- 15 Days

SeekIC Buyer Protection PLUS - newly updated for 2013!

- Escrow Protection.

- Guaranteed refunds.

- Secure payments.

- Learn more >>

Month Sales

268 Transactions

Payment Methods

All payment methods are secure and covered by SeekIC Buyer Protection PLUS.

DS060 Data Sheet

DS060 Data Sheet