Features: ·78MSPS Operation

·Low Power, 145mW/channel, 52 MHz, Dec=192

·Two Independent Channels with 14-bit inputs

·Serial Daisy-chain Mode for quad receivers

·Greater than 100 dB image rejection

·Greater than 100 dB spurious free dynamic range

·0.02 Hz tuning resolution

·User Programmable AGC with enhanced Power Detector

·Channel Filters include a Fourth Order CIC followed by 21-tap and 63-tap Symmetric FIRs

·FIR filters process 21-bit Data with 16-bit Programmable Coefficients

·Two independent FIR coefficient memories which can be routed to either or both channels.

·Flexible output formats include 12-bit Floating Point or 8, 16, 24, and 32 bit Fixed Point

·Serial and Parallel output ports

·JTAG Boundary Scan

·8-bit Microprocessor Interface

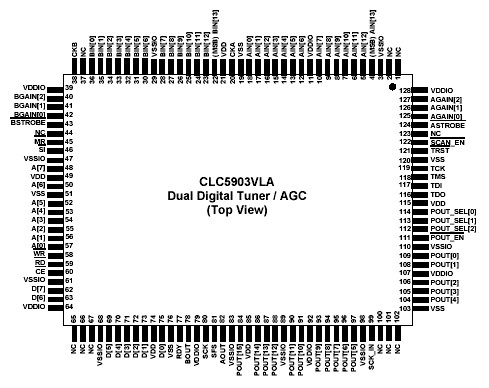

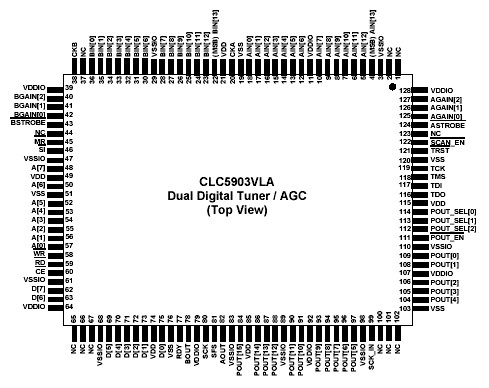

·128 pin PQFP and 128 pin FBGA packages

·100% Software compatible with the CLC5902

·Pin compatible with the CLC5902 except for VDD voltageApplication·Cellular Basestations

·Satellite Receivers

·Wireless Local Loop Receivers

·Digital CommunicationsPinout SpecificationsPositive IO Supply Voltage (VDDIO) -0.3V to 4.2V

SpecificationsPositive IO Supply Voltage (VDDIO) -0.3V to 4.2V

Positive CoreSupply Voltage (VDD) -0.3V to 2.4V

Voltage on Any Input or Output Pin -0.3V to VDDIO+0.5V

Input Current at Any Pin ±25mA

Package Input Current ±50mA

Package Dissipation at TA=25 1W

ESD Susceptibility

Human Body Model 2000V

Machine Model 200V

Soldering Temperature, Infrared, 10

seconds 300

Storage Temperature -65 to 150DescriptionThe CLC5903 Dual Digital Tuner / AGC IC is a two channel digital downconverter (DDC) with integrated automatic gain control (AGC). The CLC5903 is a key component in the Enhanced Diversity Receiver Chipset (EDRCS) whichin includes one CLC5903 Dual Digital Tuner / AGC, two CLC5957 12-bit analog-to-digital converters (ADCs), and two CLC5526 digitally controlled variable gain amplifiers (DVGAs). This system allows direct IF sampling of signals up to 300MHz for enhanced receiver performance and reduced system costs.

The CLC5903 is an enhanced replacement for the CLC5902 in the Diversity Receiver Chipset (DRCS). The main improvements relative to the CLC5902 are a 50% increase in maximum sample rate from 52MHz to 78MHz, a 62% reduction in power consumption from 760mW to 290mW, and the added flexibility to independently program filter coefficients in the two channels. A block diagram for a DRCS-based narrowband communications system is shown in Figure 1.

The CLC5903 offers high dynamic range digital tuning and filtering based on hard-wired digital signal processing (DSP) technology. Each channel has independent tuning, phase offset, filter coefficients, and gain settings. Channel filtering is performed by a series of three filters. The first is a 4-stage Cascaded Integrator Comb (CIC) filter with a programmable decimation ratio from 8 to 2048. Next there are two symmetric FIR filters, a 21-tap and a 63-tap, both with independent programmable coefficients. The first FIR filter decimates the data by 2, the second FIR decimates by either 2 or 4. Channel filter bandwidth at 52MSPS ranges from ±650kHz down to ±1.3kHz. At 78MSPS, the maximum bandwidth increases to ±975kHz.

The CLC5903's AGC controller monitors the ADC output and controls the ADC input signal level by adjusting the DVGA setting. AGC threshold, deadband+hysteresis, and the loop time constant are user defined. Total dynamic range of greater than 120dB full-scale signal to noise in a 200kHz bandwidth can be achieved with the Diversity Receiver Chipset.

CLC5903 Data Sheet

CLC5903 Data Sheet