Features: • Compatible with MCS®51 Products

• 20 MIPS Throughput at 20 MHz Clock Frequency and 2.7V, 85°C Operating Conditions

• Single Clock Cycle per Byte Fetch

• 2/4K Bytes of In-System Programmable (ISP) Flash Memory

Serial Interface for Program Downloading

32-byte Fast Page Programming Mode

32-byte User Signature Array

• 2.4V to 5.5V VCC Operating Range

• Fully Static Operation: 0 Hz to 20 MHz

• 2-level Program Memory Lock

• 256 x 8 Internal RAM

• Hardware Multiplier

• 15 Programmable I/O Lines

• Configurable I/O with Quasi-bidirectional, Input, Push-pull Output, and Open-drain Modes

• Enhanced UART with Automatic Address Recognition and Framing Error Detection

• Enhanced SPI with Double-buffered Send/Receive

• Programmable Watchdog Timer with Software Reset

• 4-level Interrupt Priority

• Analog Comparator with Selectable Interrupt and Debouncing

• Two 16-bit Enhanced Timer/Counters with 8-bit PWM

• Brown-out Detector and Power-off Flag

• Internal Power-on Reset

• Low Power Idle and Power-down Modes

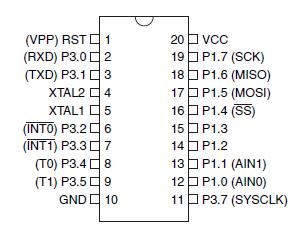

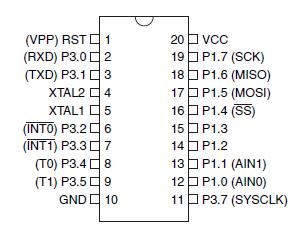

• Interrupt Recovery from Power-down ModePinout Specifications

SpecificationsOperating Temperature ................................. -55°C to +125°C

Storage Temperature .................................... -65°C to +150°C

Voltage on Any Pin with Respect to Ground.......-0.7V to +6.2V

Maximum Operating Voltage ............................................ 5.5V

DC Output Current...................................................... 15.0 mA

Note: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

DescriptionThe AT89LP2052/LP4052 is a low-power, high-performance CMOS 8-bit microcontroller with 2/4K bytes of In-System Programmable Flash memory. The device is manufactured using Atmel's high-density nonvolatile memory technology and is compatible with the industry-standard MCS-51 instruction set. The AT89LP2052/LP4052 is built around an enhanced CPU core that can fetch a single byte from memory every clock cycle. In the classic 8051 architecture, each fetch required 6 clock cycles, forcing instructions to execute in 12, 24 or 48 clock cycles. In the AT89LP2052/LP4052 CPU, instructions need only 1 to 4 clock cycles providing 6 to 12 times more throughput than the standard 8051. Seventy percent of instructions need only as many clock cycles as they have bytes to execute, and most of the remaining instructions require only one additional clock. The enhanced CPU core is capable of 20 MIPS throughput whereas the classic 8051 CPU can deliver only 4 MIPS at the same current consumption. Conversely, at the same throughput as the classic 8051, the new CPU core runs at a much lower speed and thereby greatly reduces power consumption.

The two timer/counters in the AT89LP2052/LP4052 are enhanced with two new modes. Mode 0 can be configured as a variable 9- to 16-bit timer/counter and Mode 1 can be configured as a 16-bit auto-reload timer/counter. In addition both timer/counters may be configured as 8-bit Pulse Width Modulators with 8-bit prescalers.

The I/O ports of the AT89LP2052/LP4052 can be independently configured in one of four operating modes. In quasi-bidirectional mode, the ports operate as in the classic 8051. In input mode, the ports are tri-stated. Push-pull output mode provides full CMOS drivers and open-drain mode provides just a pull-down.

AT89LP2052 Data Sheet

AT89LP2052 Data Sheet