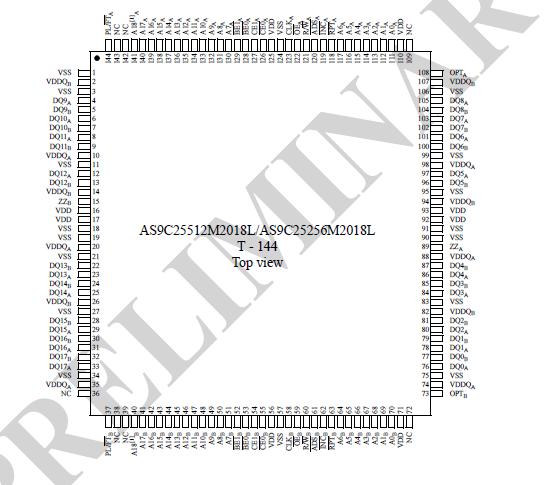

AS9C25512M2018L: Features: • True Dual-Port memory cells that allow simultaneous access of the same memory location• Organisation: 524,288/262,144 × 18[1]• Fully Synchronous, independent operation ...

floor Price/Ceiling Price

- Part Number:

- AS9C25512M2018L

- Supply Ability:

- 5000

Price Break

- Qty

- 1~5000

- Unit Price

- Negotiable

- Processing time

- 15 Days

SeekIC Buyer Protection PLUS - newly updated for 2013!

- Escrow Protection.

- Guaranteed refunds.

- Secure payments.

- Learn more >>

Month Sales

268 Transactions

Payment Methods

All payment methods are secure and covered by SeekIC Buyer Protection PLUS.

AS9C25512M2018L Data Sheet

AS9C25512M2018L Data Sheet