Features: • True Dual-Port memory cells that allow simultaneous access of the same memory location

• Organisation: 262,144/131,072 x 36[1]

• Fully Synchronous, independent operation on both ports

• Selectable Pipeline or Flow-Through output mode

• Fast clock speeds in Pipeline output mode: 250 MHz operation (18Gbps bandwidth)

• Fast clock to data access: 2.8ns for Pipeline output mode

• Asynchronous output enable control

• Fast OE access times: 2.8ns

• Double Cycle Deselect (DCD) for Pipeline Output Mode

• 18/17[1]-bit counter with Increment, Hold and Repeat features on each port

• Dual Chip enables on both ports for easy depth expansion

• Interrupt and Collision Detection Features

• 2.5 V power supply for the core

• LVTTL compatible, selectable 3.3V or 2.5V power supply for I/Os, addresses, clock and control signals on each port

• Snooze modes for each port for standby operation

• 15mA typical standby current in power down mode

• Available in 256-pin Ball Grid Array

(BGA), 208-pin Plastic Quad Flatpack

(PQFP) and 208-pin fine pitch Ball Grid Array (fpBGA)

• Supports JTAG features compliant with IEEE 1149.1

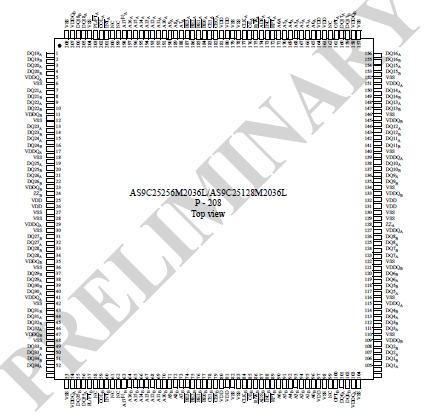

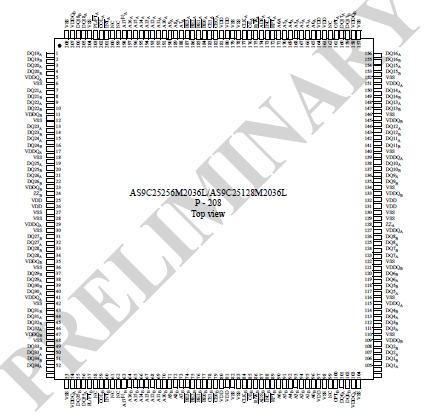

Pinout Specifications

Specifications

| Parameter |

Symbol |

Rating |

Unit |

|

Min |

Max |

| Core supply voltage relative to VSS |

VDD |

-0.5 |

3.6 |

V |

| I/O supply voltage relative to VSS |

VDDQ |

-0.3 |

3.9 |

V |

| Input and I/O voltage relative to VSS |

VIN |

-0.3 |

VDDQ + 0.3 |

V |

| Power Dissipation |

PD |

- |

TBD |

W |

| Short circuit output current |

IOUT |

- |

TBD |

mA |

| Storage Temperature |

TSTG |

-65 |

150 |

°C |

| Storage Temperature under Bias |

TBIAS |

-55 |

125 |

°C |

| Junction Temperature |

TJN |

- |

TBD |

°C |

Notes:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating for extended periods may affect reliability.DescriptionThe AS9C25256M2036L/AS9C25128M2036L is a high-speed CMOS 9/4.5-Mbit synchronous Dual-Port Static Random Access Memory device, organized as 262,144/131,072 x 36 bits. It incorporates a selectable Flow-Through/Pipeline output feature for user flexibility. Clockto- data valid time is 2.8ns at 250 MHz for "Pipeline output" mode of operation.

Each port contains an 18/17 bit linear burst counter on the input address register that can loop through the whole address sequence. After externally loading the counter with the initial address, AS9C25128M2036L can be Incremented or Held for the next cycle. A new address of AS9C25128M2036L can also be Loaded or the "Previous Loaded" address can be re-accessed (Repeated) using counter controls (More description to follow). The Registers on control, data, and address inputs provide minimal setup and hold times.

The memory array utilizes Dual-Port memory cells to allow simultaneous access of any address from both ports. A particular port can write to a certain location while another port is reading from the same location, but the validity of read data is not guaranteed. However, the reading port of AS9C25128M2036L is informed about the possible collision through AS9C25128M2036L collision alert signal. The result of writing to the same location by more than one port at the same time is undefined.

The Asynchronous Output Enable input pin allows asynchronous disabling of output buffers at any given time. The Byte Enable inputs allow individual byte ead/write operations (refer Byte Control Truth Table). An automatic power down feature, controlled by COE and CE1,permits the on-chip circuitry of each port to enter a very low standby power mode.

AS9C25256M2036L/AS9C25128M2036L can support an operating voltage of either 3.3V or 2.5V on either or both ports, which is controlled by the OPT pins. The power supply for the core of the device (VDD) is at 2.5V. This device is available in 256-pin Ball Grid Array (BGA), 208-pin fine pitch Ball Grid Array (fpBGA) and 208-pin Plastic Quad Flatpack (PQFP)

AS9C25128M2036L Data Sheet

AS9C25128M2036L Data Sheet