Features: `Up to 600MHz High-Performance Blackfin Processor

Two 16-Bit MACs, Two 40-Bit ALUs, Four 8-Bit Video ALUs, 40-Bit Shifter

RISC-Like Register and Instruction Model for Ease of Programming and Compiler-Friendly Support

Advanced Debug, Trace, and Performance-Monitoring

`0.8V to 1.2V Core VDD with On-chip Voltage Regulation

`2.5 V and 3.3 V-Tolerant I/O with Specific 5 V-Tolerant Pins

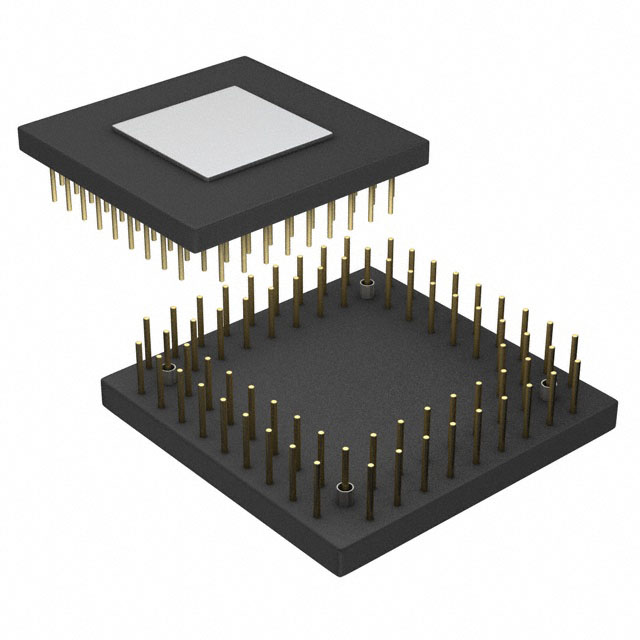

`182-Ball MBGA and 208-Ball Sparse MBGA Packages

`Lead Bearing and Lead Free Package ChoicesSpecificationsInternal (Core) Supply Voltage1 (VDDINT)0.3 V to +1.4 V

External (I/O) Supply Voltage1 (VDDEXT) 0.3 V to +3.8 V

Input Voltage1 ........................................0.5 V to +3.6 V

Output Voltage Swing1............... 0.5 V to VDDEXT+0.5 V

Load Capacitance1,2..............................................200 pF

Storage Temperature Range1 ..............65ºC to +150ºC

Junction Temperature Underbias1 ........................+125ºC

1 Stresses greater than those listed above may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2 For proper SDRAM controller operation, the maximum load capacitance is 50 pF (at 3.3V) or 30 pF (at 2.5V) for ADDR191, DATA150, ABE10/SDQM10, CLKOUT, SCKE, SA10, SRAS, SCAS, SWE, and SMS.

DescriptionThe ADSP-BF536/BF537 processors are members of the Blackfin family of products, incorporating the Analog Devices/Intel Micro Signal Architecture (MSA). Blackfin processors combine a dual-MAC state-of-the-art signal processing engine, the advantages of a clean, orthogonal RISC-like microprocessor instruction set, and single-instruction, multiple-data (SIMD) multimedia capabilities into a single instruction-set architecture.

The ADSP-BF536/BF537 processors are completely code and pin compatible, differing only with respect to their performance and on-chip memory. Specific performance and memory configurations are shown in Table 1.

ADSP-BF536 Data Sheet

ADSP-BF536 Data Sheet