Features: Complete Single Device Multi-Port Internet Gateway Processor (No External Memory Required)

Implements Sixteen Modem Channels or Forty Voice Channels in One Package

Each DSP Can Implement two V.34/V.90 Data/Fax Modem Channels (includes Datapump and Controller)

Low Power Version: 640 MIPS Sustained Performance, 12.5 ns Instruction Time @ 1.9 Volts nominal (internal)

Open Architecture Extensible to Voice-over-Network (VoN) and Other Applications

Low Power Dissipation, 25 mW (typical) per Channel

Powerdown Mode Featuring Low CMOS Standby Power Dissipation

ADSP-2100 Family Code-Compatible, with Instruction Set Extensions

16 Mbits of On-Chip SRAM, Configured as 9 Mbits of Program Memory and 7 Mbits of Data Memory

Dual-Purpose Program Memory, for Both Instruction and Data Storage

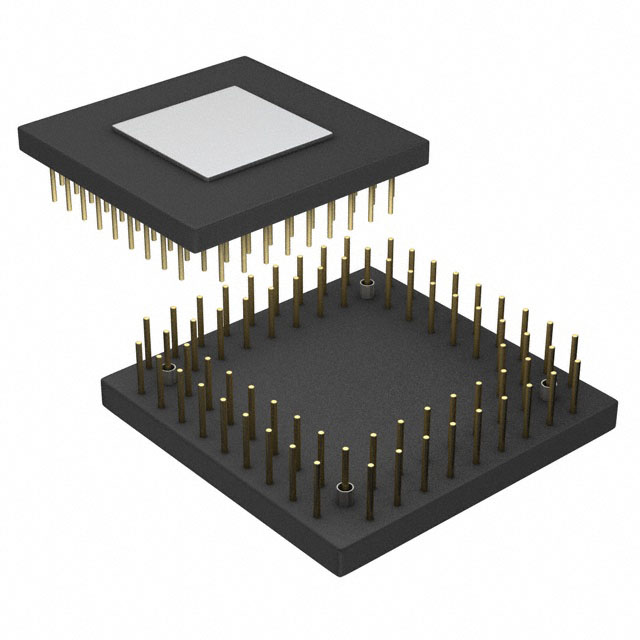

352-Ball PBGA with a 35mm 35mm footprint

16-Bit Internal DMA Port for High-Speed Access to On-Chip Memory (Mode-Selectable)

Programmable Multichannel Serial Port Supports 24/32 Channels

Two Double-Buffered Serial Ports with Companding Hardware and Automatic Data Buffering

Separate Reset Pins for Each Internal Processor

Pinout Specifications

Specifications

| Parameter |

Description |

Min. |

Max |

Unit |

VDDINT

VDDEXT |

Internal Supply Voltage

External Supply Voltage

Input Voltage1

Output Voltage Swing2

Storage Temperature Range |

0.3

0.3

0.5

0.5

65 °C |

+2.5

+4.6

+4.6

VDDEXT + 0.5

+150 °C |

V

V

V

V

°C |

DescriptionThe ADSP-21mod980N is a multi-port Internet gateway processor optimized for implementation of a complete V.34/V.90 digital modem. All datapump and controller unctions can be implemented on a single device, offering he lowest power consumption and highest possible modem port density.

The ADSP-21mod980N combines the ADSP-2100 Family base architecture (three computational units, data address generators, and a program sequencer) with two serial ports, a 16-bit internal DMA port, a byte DMA port, a program-mable timer, Flag I/O, extensive interrupt capabilities, and on-chip program and data memory. The ADSP-21mod980N integrates 16 Mbits of on-chip memory, configured as 384 Kwords (24-bit) of program RAM, and 448 Kwords (16-bit) of data RAM. Power-down circuitry is also provided to reduce the average and standby power consumption of equipment which in turn reduces equipment cooling requirements.

The ADSP-21mod980N s available in a 35 mm x 35 mm, 352-lead PBGA package.Fabricated in a high-speed, low-power, CMOS process, the ADSP-21mod980N operates with a 12.5 ns instruction cycle time. Every instruction can execute in a single proces-sor cycle. The ADSP-21mod980N's flexible architecture and com-prehensive instruction set allow the processor to perform multiple operations in parallel. In one processor cycle, the product can:

Generate the next program address

Fetch the next instruction

Perform one or two data moves

Update one or two data address pointers

Perform a computational operation

This takes place while the processor continues to:

Receive and transmit data through the two serial ports

Receive and/or transmit data through the internal DMA port

Receive and/or transmit data through the byte DMA port

Decrement timer

ADSP-21mod980N Data Sheet

ADSP-21mod980N Data Sheet