Features: 6.25 ns Instruction Cycle Time, for up to 160 MIPS

Sustained Performance

ADSP-218x Family Code Compatible with the Same

Easy to Use Algebraic Syntax

Single-Cycle Instruction Execution

Single-Cycle Context Switch between Two Sets of Computation

and Memory Instructions

Instruction Cache Allows Dual Operand Fetches in Every

Instruction Cycle

Multifunction Instructions

Pipelined Architecture Supports Efficient Code

Execution

Architectural Enhancements for Compiled C and C++

Code Efficiency

Architectural Enhancements beyond ADSP-218x Family

are Supported with Instruction Set Extensions for

Added Registers, and Peripherals

Flexible Power Management with User-Selectable

Power-Down and Idle Modes

160 K Bytes On-Chip RAM Configured as 32K Words 24-Bit

Memory RAM and 32K Words 16-Bit Memory RAM

Dual-Purpose 24-Bit Memory for Both Instruction and

Data Storage

Independent ALU, Multiplier/Accumulator, and Barrel

Shifter Computational Units with Dual 40-bit

Accumulators

Unified Memory Space Allows Flexible Address Generation,

Using Two Independent DAG Units

Powerful Program Sequencer Provides Zero-Overhead

Looping and Conditional Instruction Execution

Enhanced Interrupt Controller Enables Programming of

Interrupt Priorities and Nesting Modes

SYSTEM INTERFACE FEATURES

Host Port with DMA Capability for Glueless 8- or 16-Bit

Host Interface

16-Bit External Memory Interface for up to 16M Words of

Addressable Memory Space

Three Full-Duplex Multichannel Serial Ports, with

Support for H.100 and up to 128 TDM Channels with

A-Law and �-Law Companding Optimized for Telecommunications

Systems

Two SPI-Compatible Ports with DMA Support

UART Port with DMA Support

16 General-Purpose I/O Pins with Integrated Interrupt

Support

Three Programmable Interval Timers with PWM

Generation, PWM Capture/Pulsewidth Measurement,

and External Event Counter Capabilities

Up to 11 DMA Channels Can Be Active at Any Given Time

for High I/O Throughput

On-Chip Boot ROM for Automatic Booting from External

8- or 16-Bit Host Device, SPI ROM, or UART with

Autobaud Detection

Programmable PLL Supports 1� to 32� Input Frequency

Multiplication and Can Be Altered during Runtime

IEEE JTAG Standard 1149.1 Test Access Port Supports

On-Chip Emulation and System Debugging

2.5 V Internal Operation and 3.3 V I/O

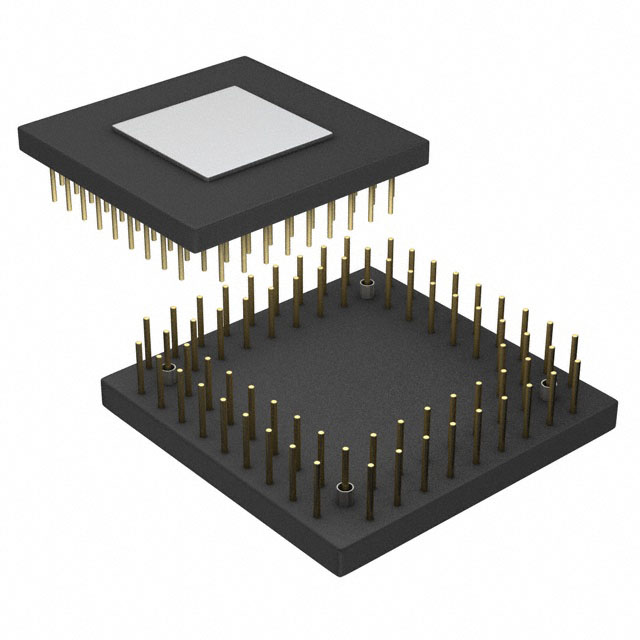

144-Lead LQFP and 144-Ball Mini-BGA PackagesSpecificationsVDDINT Internal (Core) Supply Voltage1,2. . . . 0.3 V to 3.0 V

VDDEXT External (I/O) Supply Voltage . . . . . . 0.3 V to 4.6 V

VILVIH Input Voltage . . . . . .. . . . . 0.5 V to VDDEXT+0.5 V

VOLVOH Output Voltage Swing. . . .0.5 V to VDDEXT+0.5 V

TSTOREStorage Temperature Range . . . . .. . . .65 to 150

TLEADLead Temperature of ST-144 (5 seconds) . . . .. . . 185DescriptionThe ADSP-2191M DSP is a single-chip microcomputer optimized for digital signal processing (DSP) and other high speed numeric processing applications.

The ADSP-2191M combines the ADSP-219x family base architecture (three computational units, two data address generators,and a program sequencer) with three serial ports, two SPI-compatible ports, one UART port, a DMA controller, three programmable timers, general-purpose Programmable Flag pins, extensive interrupt capabilities, and on-chip program and data memory spaces.

The architecture is code-compatible with DSPs of the ADSP-218x family. Although the architectures are compatible, the architecture has a number of enhancements over the ADSP-218x architecture. The enhancements to computational units, data address generators, and program sequencer make the ADSP-2191M more flexible and even easier to program. Indirect addressing options provide addressing flexibility-premodify with no update, pre- and post-modify by an immediate 8-bit, two's-complement value and base address registers for easier implementation of circular buffering.

The ADSP-2191M integrates 64K words of on-chip memory configured as 32K words (24-bit) of program RAM, and 32K words (16-bit) of data RAM. Power-down circuitry is also provided to reduce power consumption. It is available in 144-lead LQFP and 144-ball mini-BGA packages. Fabricated in a high-speed, low-power, CMOS process, the ADSP-2191M operates with a 6.25 ns instruction cycle time (160 MIPS). All instructions, except single-word instructions,execute in one processor. The ADSP-2191M's flexible architecture and comprehensive instruction set support multiple operations in parallel. For example, in one processor cycle, the ADSP-2191M can:

• Generate an address for the next instruction fetch

• Fetch the next instruction

• Perform one or two data moves

• Update one or two data address pointers

• Perform a computational operation These operations take place while the processor continues to:

• Receive and transmit data through two serial ports

• Receive and/or transmit data from a Host

• Receive or transmit data through the UART

• Receive or transmit data over two SPI ports

• Access external memory through the external memory interface

• Decrement the timers

The ADSP-2191M assembly language instruction set has an algebraic syntax that was designed for ease of coding and readability. The assembly language, which takes full advantage of the processor's unique architecture, offers the following benefits:

• ADSP-219x assembly language syntax is a superset of and source-code-compatible (except for two data registers and DAG base address registers) with ADSP-218x family syntax. It may be necessary to restructure ADSP-218x programs to accommodate the ADSP-2191M's unified memory space and to conform to its interrupt vector map.

• The ADSP-2191M algebraic syntax eliminates the need to remember cryptic assembler mnemonics. For example, a typical arithmetic add instruction, such as AR = AX0 + AY0,resembles a simple equation.

• Every instruction, but two, assembles into a single, 24-bit word that can execute in a single instruction cycle. The ADSP-2191M exceptions are two dual word instructions. One writes 16- or 24-bit immediate data to memory, and the other is an absolute jump/call with the 24-bit address specified in the instruction.

• Multifunction instructions of ADSP-2191M allow parallel execution of an arithmetic, MAC, or shift instruction with up to two fetches or one write to processor memory space during a single instruction cycle.

• Program flow instructions of ADSP-2191M support a wider variety of conditional and unconditional jumps/calls and a larger set of conditions on which to base execution of conditional instructions.

ADSP-2191M Data Sheet

ADSP-2191M Data Sheet