Features: `Performance

`13.3 ns Instruction Cycle Time @ 2.75 V (Internal), 75 MIPS Sustained Performance

`Single-Cycle Instruction Execution

`Single-Cycle Context Switch

`3-Bus Architecture Allows Dual Operand Fetches in Every Instruction Cycle

`Multifunction Instructions

`Power-Down Mode Featuring Low CMOS Standby Power Dissipation with 200 CLKIN Cycle Recovery from Power-Down Condition

`Low Power Dissipation in Idle Mode

`Integration

`ADSP-2100 Family Code Compatible (Easy to Use Algebraic Syntax), with Instruction Set Extensions

`256K Bytes of On-Chip RAM, Configured as 48K Words Program Memory RAM 56K Words Data Memory RAM

`Dual-Purpose Program Memory for Both Instruction and Data Storage

`Independent ALU, Multiplier/Accumulator, and Barrel Shifter Computational Units

`Two Independent Data Address Generators

`Powerful Program Sequencer Provides Zero Overhead Looping Conditional Instruction Execution

`Programmable 16-Bit Interval Timer with Prescaler

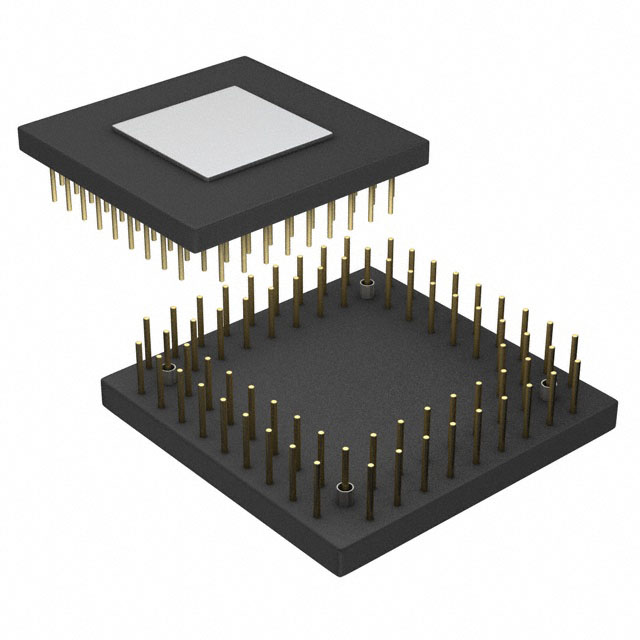

`100-Lead LQFP and 144-Ball Mini-BGA

`System Interface

`Flexible I/O Structure Allows 2.75V or 3.3 V Operation; All Inputs Tolerate up to 3.6 V Regardless of Mode

`16-Bit Internal DMA Port for High-Speed Access to On-Chip Memory (Mode Selectable)

`4 MByte Memory Interface for Storage of Data Tables and Program Overlays (Mode Selectable)

`8-Bit DMA to Byte Memory for Transparent Program and Data Memory Transfers (Mode Selectable)

`I/O Memory Interface with 2048 Locations Supports

`Parallel Peripherals (Mode Selectable) Programmable Memory Strobe and Separate I/O Memory Space Permits "Glueless" System Design

`Programmable Wait State Generation

`Two Double-Buffered Serial Ports with Companding Hardware and Automatic Data Buffering

`Automatic Booting of On-Chip Program Memory from Byte-Wide External Memory, e.g., EPROM, or through Internal DMA Port

`Six External Interrupts

`13 Programmable Flag Pins Provide Flexible System Signaling

`UART Emulation through Software SPORT Reconfiguration

`ICE-Port™ Emulator Interface Supports Debugging in Final SystemsSpecifications

|

Parameter |

Value |

|

Min |

Max |

Internal Supply Voltage (VDDINT)

External Supply Voltage (VDDEXT)

Input Voltage2

Output Voltage Swing3

Operating Temperature Range

Storage Temperature Range

Lead Temperature (5 sec) LQFP |

0.3 V

0.3 V

0.5 V

0.5 V

40°C

65°C |

+3.0 V

+4.0 V

+4.0 V

VDDEXT + 0.5 V

+85°C

+150°C

280°C |

NOTES

1Stresses greater than those listed may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2Applies to Bidirectional pins (D0D23, RFS0, RFS1, SCLK0, SCLK1, TFS0, TFS1, A1A13, PF0PF7) and Input only pins (CLKIN, RESET, BR, DR0, DR1, PWD).

3Applies to Output pins (BG, PMS, DMS, BMS, IOMS, CMS, RD, WR, PWDACK, A0, DT0, DT1, CLKOUT, FL20, BGH).

DescriptionThe ADSP-2188M is a single-chip microcomputer optimized for digital signal processing (DSP) and other high-speed numeric processing applications.

The ADSP-2188M combines the ADSP-2100 family base architecture (three computational units, data address generators, and a program sequencer) with two serial ports, a 16-bit internal DMA port, a byte DMA port, a programmable timer, Flag I/O, extensive interrupt capabilities, and on-chip program and data memory.

The ADSP-2188M integrates 256K bytes of on-chip memory configured as 48K words (24-bit) of program RAM, and 56K words (16-bit) of data RAM. Power-down circuitry is also provided to meet the low power needs of battery-operated portable equipment. It is available in a 100-lead LQFP package and 144 Ball Mini-BGA.

In addition, the ADSP-2188M supports new instructions, which include bit manipulations-bit set, bit clear, bit toggle, bit test- new ALU constants, new multiplication instruction (* squared), biased rounding, result-free ALU operations, I/O memory transfers, and global interrupt masking, for increased flexibility. Fabricated in a high-speed, low-power, CMOS process, the ADSP-2188M operates with a 13.3 ns instruction cycle time. Every instruction can execute in a single processor cycle.

The ADSP-2188M's flexible architecture and comprehensive instruction set allow the processor to perform multiple operations in parallel. In one processor cycle:

• Generate the next program address

• Fetch the next instruction

• Perform one or two data moves

• Update one or two data address pointers

• Perform a computational operation This takes place while the processor continues to:

• Receive and transmit data through the two serial ports

• Receive and/or transmit data through the internal DMA port

• Receive and/or transmit data through the byte DMA port

• Decrement timer

The ADSP-2189M EZ-KIT Lite is a low cost, easy to use hardware platform on which you can quickly get started with your DSP software design.

The EZ-KIT Lite includes the following features:

• 75 MHz ADSP-2189M

• Full 16-Bit Stereo Audio I/O with AD73322 Codec

• RS-232 Interface

• EZ-ICE Connector for Emulator Control

• DSP Demo Programs

• Evaluation Suite of VisualDSP

The ADSP-218x EZ-ICE® Emulator aids in the hardware debugging of an ADSP-2188M system. It integrates on-chip emulation support with a 14-pin ICE-Port interface. This interface provides a simpler target board connection that requires fewer mechanical clearance considerations than other ADSP-2100 Family EZ-ICEs. The ADSP-2188M device need not be removed from the target system when using the EZ-ICE, nor are any adapters needed. Due to the small footprint of the EZ-ICE connector, emulation can be supported in final board designs.

The EZ-ICE performs a full range of functions, including:

• In-target operation • Up to 20 breakpoints

• Single-step or full-speed operation

• Registers and memory values can be examined and altered

• PC upload and download functions

• Instruction-level emulation of program booting and execution

• Complete assembly and disassembly of instructions

• C source-level debugging

See Designing An EZ-ICE-Compatible Target System in the ADSP-2100 Family EZ-Tools Manual (ADSPADSP-2188M) as well as the Designing an EZ-ICE-Compatible System section of this data sheet for the exact specifications of the EZ-ICE target board connector.

ADSP-2188M Data Sheet

ADSP-2188M Data Sheet