Features: 25 ns Instruction Cycle Time from 20 MHz Crystal @ 5.0 Volts

40 MIPS Sustained Performance

Single-Cycle Instruction Execution

Single-Cycle Context Switch

3-Bus Architecture Allows Dual Operand Fetches in

Every Instruction Cycle

Multifunction Instructions

Power-Down Mode Featuring Low CMOS Standby

Power Dissipation with 100 Cycle Recovery from

Power-Down Condition

Low Power Dissipation in Idle ModePinout SpecificationsSupply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . .0.3 V to +7 V

SpecificationsSupply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . .0.3 V to +7 V

Input Voltage . . . . . . . . . . . . . . . . . . . . . .0.3 V to VDD + 0.3 V

Output Voltage Swing . . . . . . . . . . . . . . .0.3 V to VDD + 0.3 V

Operating Temperature Range (Ambient) . . . . 40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . . 65°C to +150°C

Lead Temperature (5 sec) TQFP . . . . . . . . . . . . . . . . . . +280°C

Lead Temperature (5 sec) PQFP . . . . . . . . . . . . . . . . . . .+280°CDescriptionThe ADSP-2181 is a single-chip microcomputer optimized for digital signal processing (DSP) and other high speed numeric processing applications.

The ADSP-2181 combines the ADSP-2100 family base architecture (three computational units, data address generators and a program sequencer) with two serial ports, a 16-bit internal DMA port, a byte DMA port, a programmable timer, Flag I/O, extensive interrupt capabilities, and on-chip program and data memory.

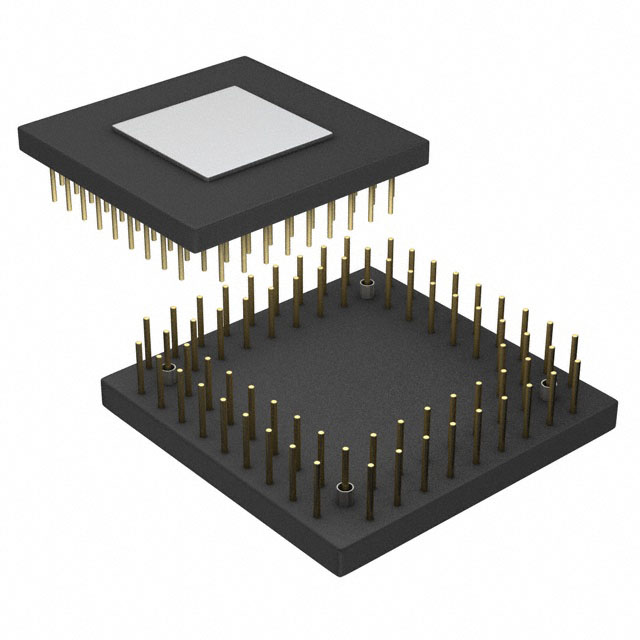

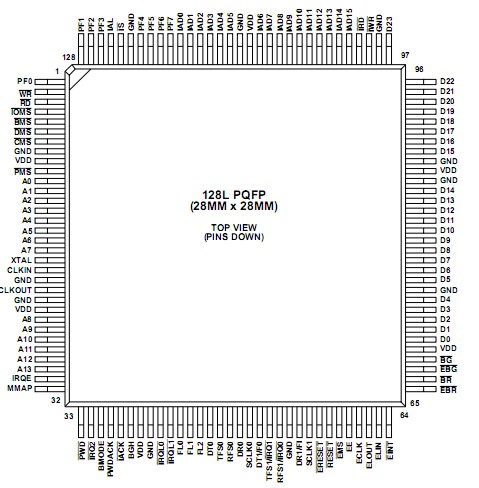

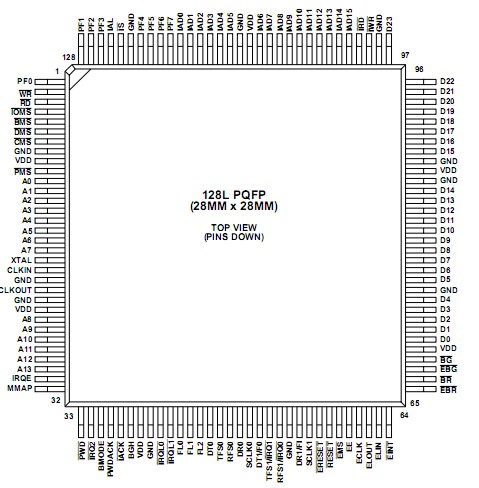

The ADSP-2181 integrates 80K bytes of on-chip memory configured as 16K words (24-bit) of program RAM, and 16K words (16-bit) of data RAM. Power-down circuitry is also provided to meet the low power needs of battery operated portable equipment. The ADSP-2181 is available in 128-lead TQFP and 128-lead PQFP packages.

In addition, the ADSP-2181 supports new instructions, which include bit manipulations-bit set, bit clear, bit toggle, bit test-new ALU constants, new multiplication instruction (x squared), biased rounding, result free ALU operations, I/O memory transfers and global interrupt masking for increased flexibility.

Fabricated in a high speed, double metal, low power, CMOS process, the ADSP-2181 operates with a 25 ns instruction cycle time. Every instruction can execute in a single processor cycle.

The ADSP-2181's flexible architecture and comprehensive instruction set allow the processor to perform multiple operations in parallel. In one processor cycle:

• Generate the next program address

• Fetch the next instruction

• Perform one or two data moves

• Update one or two data address pointers

• Perform a computational operation

ADSP-2181KST Data Sheet

ADSP-2181KST Data Sheet