Features: ·95MHz (10.5ns) Core Instruction Rate

·Single-Cycle Instruction Execution, Including SIMD

·Operations in Both Computational Units

·570MFLOPS Peak and 380MFLOPS Sustained

·Performance (Based on FIR)

·Dual Data Address Generators (DAGs) with Modulo and

·Bit-Reverse Addressing

·Zero-Overhead Looping and Single-Cycle Loop Setup,

·Providing Efficient Program Sequencing

·IEEE 1149.1 JTAG Standard Test Access Port and

·On-Chip Emulation

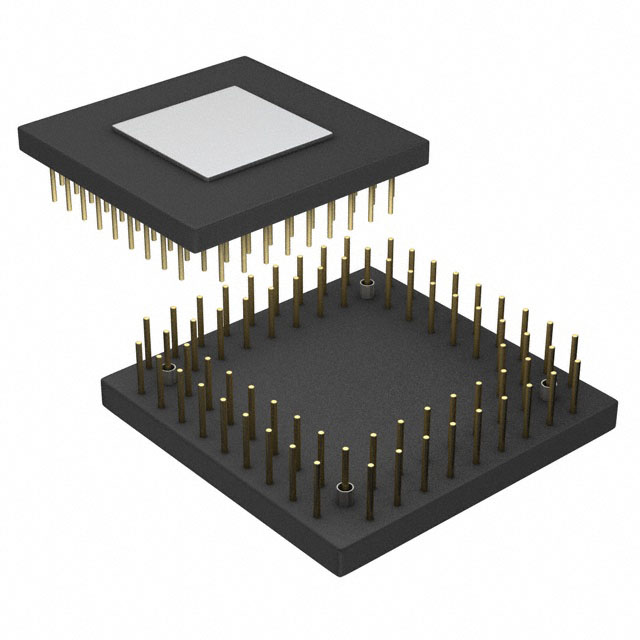

·400-Ball 27 27mm Metric PBGA PackageSpecificationsInternal (Core) Supply Voltage (VDDINT )1. . . . . . -0.3 V to +2.3 V

Analog (PLL) Supply Voltage (AVDD). . . . . . . . . . . -0.3 V to +2.3 V

External (I/O) Supply Voltage (VDDEXT). . . . . . . . .-0.3 V to +4.6 V

Input Voltage . . . . . . . . . . . . . . . . . . . . . .-0.5V to VDDEXT +0.5 V

Output Voltage Swing . . . . . . . . . . . . . . . -0.5V to VDDEXT +0.5 V

Load Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200pF

Junction Temperature under Bias. . . . . . . . . . . . . . . . . . . . . 130

Storage Temperature Range. . . . . . . . . . . . . . . . -65 to +150

1 Stresses greater than those listed above may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

DescriptionThe ADSP-21160N SHARC DSP is the second iteration of the ADSP-21160. Built in a 0.18 micron CMOS process, it offers higher performance and lower power consumption than its predecessor, the ADSP-21160M. Easing portabil-ity, it is application source code compatible with first generation ADSP-2106x SHARC DSPs in SISD (Single Instruction, Single Data) mode. To take advantage of the processor!s SIMD (Singe Instruction, Multiple Data) capability, some code changes are needed. Like other SHARCs, the ADSP-21160N is a 32-bit processor that is optimized for high performance DSP appli- cations. The ADSP-21160N includes an 95 MHz core, a dual-ported on-chip SRAM, an integrated I/O processor with multiprocessing support, and multiple internal buses to eliminate I/O bottlenecks.

The product introduces Single-Instruction, Multiple-Data (SIMD) processing. Using two computa- tional units (ADSP-2106x SHARC DSPs have one), the ADSP-21160N can double performance versus the ADSP-2106x on a range of DSP algorithms.

Fabricated in a state of the art, high speed, low power CMOS process, the ADSP-21160N has a 10.5ns instruc- tion cycle time. With its SIMD computational hardware running at 95MHz, the product can perform 570 million math operations per second.

ADSP-21160N Data Sheet

ADSP-21160N Data Sheet