Features: •5-volt tolerant inputs/outputs, for interfacing with 5-volt logic

•Supply voltage range of 2.7V to 3.6V

•Complies with JEDEC standard no. 8-1A

•Inputs accept voltages up to 5.5V

•CMOS low power consumption

•Direct interface with TTL levels

•9-bit positive edge-triggered register

•Independent register and 3-State buffer operation

•Flow-through pin-out architecture

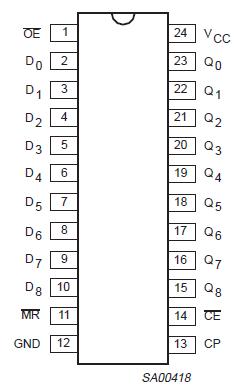

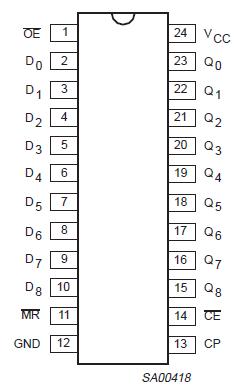

Pinout Specifications

Specifications

| SYMBOL |

PARAMETER |

CONDITIONS |

RATING |

UNIT |

| VCC |

DC supply voltage |

|

0.5 to +6.5 |

V |

| IIK |

DC input diode current |

VI0 |

50 |

mA |

| VI |

DC input voltage |

Note 2 |

0.5 to +5.5 |

V |

| VI/O |

DC input voltage range for I/Os |

|

0.5toVCC+0.5 |

V |

| IOK |

DC output diode current |

VOVCC or VO0 |

±50 |

mA |

| VOUT |

DC output voltage; output HIGH or LOW |

Note 2 |

0.5 to VCC +0.5 |

V |

| VOUT |

DC output voltage; output 3-State |

Note 2 |

0.5 to +6.5 |

V |

| IOUT |

DC output source or sink current |

VO = 0 to VCC |

±50 |

mA |

| IGND,ICC |

DC VCC or GND current |

|

±100 |

mA |

| Tstg |

Storage temperature range |

|

60 to +150 |

|

| PTOT |

Power dissipation per package

plastic mini-pack (SO)

plastic shrink mini-pack (SSOP and TSSOP) |

above+70°Cderatelinearlywith8mW/K

above +60°C deratelinearlywith5.5mW/K |

500

500 |

mW |

DescriptionThe 74LVC823A is a high performance, low-power, low-voltage

Si-gate CMOS device and superior to most advanced CMOS compatible TTL families.

Inputs can be driven from either 3.3V or 5.0V devices. In 3-state operation, outputs can handle 5V. This feature allows the use of these devices as translators in a mixed 3.3V/5V environment.

The 74LVC823A is a 9-bit D-type flip-flop with common clock (CP), Clock Enable (CE), Master Reset (MR) and 3-State outputs for bus-oriented applications.

The nine flip-flops will store the state of their individual D-inputs that meet the set-up and hold times requirements on the LOW-to-HIGH CP transition provided CE is LOW. When CE is HIGH the flip-flops hold their data.

A LOW on MR resets all flip-flops.

When OE of the 74LVC823A is LOW, the contents of the nine flip-flops is available at the outputs. When OE is HIGH, the outputs go to the high impedance OFF-state. Operation of the OEinput does not affect the state of the flip-flops.

74LVC823A Data Sheet

74LVC823A Data Sheet