Features: Common features: 0.5 MICRON CMOS Technology High-speed, low-power CMOS replacement forABT functions Typical tSK(o) (Output Skew) < 250ps Low input and output leakage1A (max.) ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200pF, R = 0) Packages include 25 mil pitch SSOP, 19.6 mil pitch TSSOP, 15.7 mil pitch TVSOP and 25 mil pitch Cerpack Extended commercial range of -40°C to +85°C VCC = 5V ±10%

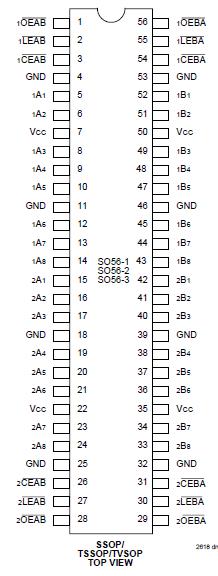

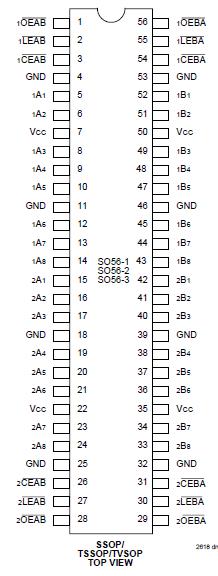

Pinout Specifications

Specifications

| Symbol |

Description |

Max. |

Unit |

| VTERM(2) |

Terminal Voltage with Respect to

GND |

0.5 to +7.0 |

V |

| VTERM(3) |

Terminal Voltage with Respect to

GND |

0.5 to

VCC +0.5 |

V |

| TSTG |

Storage Temperature |

65 to +150 |

|

| IOUT |

DC Output Current |

60 to +120 |

mA |

DescriptionThe 74FCT162543T 16-bit latched transceivers are built using advanced dual metal CMOS technology. These high-speed, low-power devices are organized as two independent 8-bit D-type latched transceivers with separate input and output control to permit independent control of data flow in either direction. For example, the Ato- B Enable (xCEAB) must be LOW in order to enter data from the A port or to output data from the B port. xLEAB controls the latch function. When xLEAB of the 74FCT162543T is LOW, the latches are transparent. A subsequent LOW-to-HIGH transition of xLEAB signal puts the A latches in the storage mode. xOEAB performs output enable function on the B port. Data flow from the B port to the A port is similar but requires using xCEBA, xLEBA, and xOEBA inputs. Flow-through organization of signal pins simplifies layout. All inputs are designed with hysteresis for improved noise margin.

The 74FCT162543T are ideally suited for driving high-capacitance loads and low-impedance backplanes. The output buffers are designed with power off disable capability to allow "live insertion" of boards when used as backplane drivers.

The 74FCT162543T have balanced output drive with current limiting resistors. This offers low ground bounce, minimal undershoot, and controlled output fall timesreducing the need for external series terminating resistors. The FCT162543T/AT/CT/ET are plug-in replacements for the 74FCT162543T for on-board bus interface applications.

74FCT162543T Data Sheet

74FCT162543T Data Sheet