Features: • High speed parallel latches

• Extra data width for wide address/data paths or buses carrying parity

• High impedance NPN base input structure minimizes bus loading

• IIL is 20mA vs 1000A for AM29841 series

• Buffered control inputs to reduce AC effects

• Ideal where high speed, light loading, or increased fan-in are required as with MOS microprocessors

• Positive and negative over-shoots are clamped to ground

• 3-State outputs glitch free during power-up and power-down

• 48mA sink current

• Slim dual in-line 300 mil package

• Broadside pinout

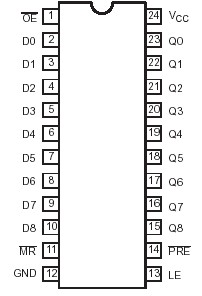

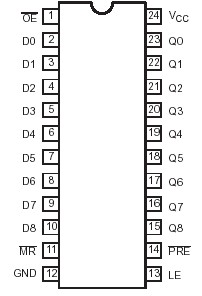

• Pin-for-pin and function compatible with AMD AM29841-846 seriesPinout

Specifications

| SYMBOL |

PARAMETER |

RATING |

UNIT |

| VCC |

Supply voltage |

0.5 to +7.0 |

V |

| VIN |

Input voltage |

0.5 to +7.0 |

V |

| IIN |

Input current |

30 to +5 |

mA |

| VOUT |

Voltage applied to output in high output state |

0.5 to VCC |

V |

| IOUT |

Current applied to output in low output state |

84 |

mA |

| Tamb |

Operating free-air temperature range |

0 to +70

|

|

| Tstg |

Storage temperature range |

65 to +150 |

|

DescriptionThe 74F843 bus interface latch series are designed to provide extra data width for wider address/data paths of buses carrying parity.

The 74F843 series are funcitonally an pin compatible to the AMD AM29841AM29846 series.

The 74F843 consists of ten D-type latches with 3-State outputs. The flip-flops appear transparent to the data when Latch Enable (LE) is High. This allows asynchronous operation, as the output transition follows the data in transition. On the LE High-to-Low transition, the data that meets the setup and hold time is latched.

Data appears on the bus when the Output Enable (OE) is Low.

When OE is High the output is in the High-impedance state.

The 74F843 is the inverted output version of the 74F841.

The 74F843 consists of nine D-type latches with 3-State outputs. In addition to the LE and OE pins, the 74F843 has a Master Reset (MR) pin and Preset (PRE) pin. These pins are ideal for parity bus interfacing in high performance systems. When MR is Low, the outputs are Low if OE is Low. When MR is High, data can be entered into the latch. When PRE is Low, the outputs are High, if OE is Low, PRE overrides MR.

The 74F843 consists of eight D-type latches with 3-State outputs. In addition to the LE, OE, MR and PRE pins, the 74F845 has two addtitional OE pins making a total of three Output Enables (OE0, OE1, OE2) pins.

The multiple Ouptut Enables (OE0, OE1, OE2) allow multi-user control of the interface, e.g., CS, DMA, and RD/WR.

The 74F843 is the inverted output version of the 74F845.

74F843 Data Sheet

74F843 Data Sheet