Features: • Up to 40 MIPS at 80MHz core frequency

• DSP and MCU functionality in a unified,

C-efficient architecture

• Hardware DO and REP loops

• MCU-friendly instruction set supports both

DSP and controller functions: MAC, bit

manipulation unit, 14 addressing modes

• 60K × 16-bit words Program Flash

• 2K × 16-bit words Program RAM

• 8K × 16-bit words Data Flash

• 4K × 16-bit words Data RAM

• 2K × 16-bit words Boot Flash

• Up to 64K × 16- bit words each of external

Program and Data memory

• Two 6 channel PWM Modules

• Four 4 channel, 12-bit ADCs

• Two Quadrature Decoders

• CAN 2.0 B Module

• Two Serial Communication Interfaces (SCIs)

• Serial Peripheral Interface (SPI)

• Up to four General Purpose Quad Timers

• JTAG/OnCETM port for debugging

• 14 Dedicated and 18 Shared GPIO lines

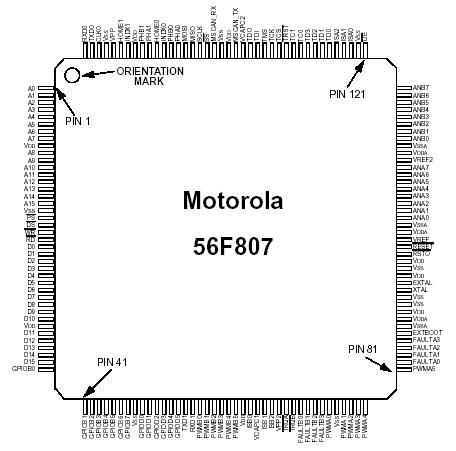

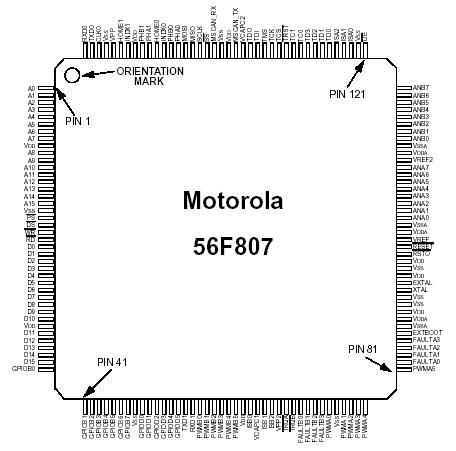

• 160-pin LQFP or 160 MAPBGA PackagesPinout Specifications

Specifications

| Characteristic |

Symbol |

Min |

Max |

Unit |

| Supply voltage |

VDD |

VSS 0.3 |

VSS + 4.0 |

V |

| All other input voltages, excluding Analog inputs |

VIN |

VSS 0.3 |

VSS + 5.5V |

V |

| Analog inputs ANA0-7 and VREF |

VIN |

VSS 0.3 |

VDDA+ 0.3 |

V |

| Analog inputs EXTAL and XTAL |

VIN |

VSS 0.3 |

VSSA+ 3.0 |

V |

| Current drain per pin excluding VDD,VSS,PWM ouputs,TCS,VPP, VDDA, VSSA |

I |

- |

10 |

mA |

DescriptionThe 56F807 is a member of the 56800 core-based family of hybrid controllers. It combines, on a single chip, the processing power of a DSP and the functionality of a microcontroller with a flexible set of peripherals to create an extremely cost-effective solution. Because of its low cost, configuration flexibility, and compact program code, the 56F807 is well-suited for many applications. The 56F807 includes many peripherals that are especially useful for applications such as motion control, smart appliances, steppers, encoders, tachometers, limit switches, power supply and control, automotive control, engine management, noise suppression, remote utility metering, industrial control for power, lighting, and automation.

The 56800 core is based on a Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set allow straightforward generation of efficient, compact DSP and control code. The instruction set of 56F807 is also highly efficient for C/C++ Compilers to enable rapid development of optimized control applications.

The 56F807 supports program execution from either internal or external memories. Two data operands can be accessed from the on-chip Data RAM per instruction cycle. The 56F807 also provides two external dedicated interrupt lines and up to 32 General Purpose Input/Output (GPIO) lines, depending on peripheral configuration.

The 56F807 controller includes 60K, 16-bit words of Program Flash and 8K words of Data Flash (each programmable through the JTAG port) with 2K words of Program RAM and 4K words of Data RAM. It also supports program execution from external memory.

56F807 Data Sheet

56F807 Data Sheet