Index 241

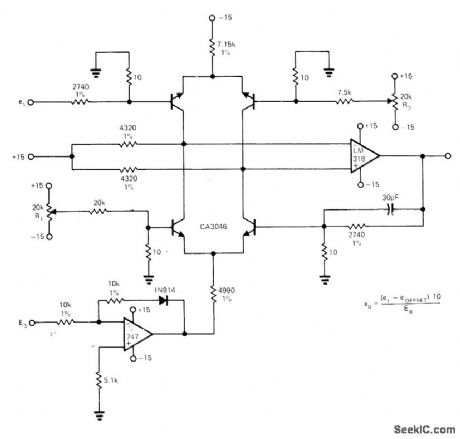

XY÷Z_CIRCUIT

Published:2009/7/7 21:54:00 Author:May

Developed for controlling amplitude of video signal from photodiode ary over 2 to 1 range. Circuit provides 3-dB band-width of 3 MHz, using CA3046 transistor array combined with LM318 opamp connected as analog divider, with half of 747 opamp sewing as current source. Article covers initial adjustments of circuit. Basic circuit may be used as full XY ÷ Z multiply/divide element with differential bipolar signals on one numerator input.-A. R. Kopp, An Analog Multiplier/Divider Circuit, EDN Magazine, May 5, 1973, p 74-75.

(View)

View full Circuit Diagram | Comments | Reading(1636)

ADD_ON_TELEPHONE_HOLD_BUTTON

Published:2009/7/7 21:52:00 Author:May

A sensitive-gate SCR provides a line-holding current of 20 to 40 mA, depending on loop resistance. It also lights an LED to give the user a positive indication that the telephone line is on hold. The 20 to 40 mA should prove sufficient to hold the majority of lines, but it might require increasing-by decreasing the size of R1-in individual instances. When any receiver in the same loop is lifted, the low impedance of the offhook telephone set shunts holding current away from the SCR, thereby releasing the line and extinguishing the LED. Zener diode D2 ensures that the line-holding current drops below the SCR's minimum conduction current. If the calling party tires of waiting on hold and hangs up, the release of the central-office relays from the calling side also releases the line from the hold mode. (View)

View full Circuit Diagram | Comments | Reading(624)

COIN_FLIPPER

Published:2009/7/7 21:47:00 Author:May

One of LEDs comes on when S1 is pressed, to simulate tossing of coin. LEDs can be labeled HEADS and TAILS if desired. Transistor types are not critical. For true random results, voltage between collectors of transistors should be 0 V with S2 closed and S1 open.-Circuits, 73 Magazine, June 1975, p 161. (View)

View full Circuit Diagram | Comments | Reading(0)

VIDEO_MODULATOR

Published:2009/7/7 21:44:00 Author:May

National LM1889N serves to interface dudio, color difference, and luminance signals to antenna terminals of TV receiver. Circuit allows video information from video games, test equipment, videotape reorders, and similar sources to be displayed on black-and-white or color TV receivers. LM1889N consists of sound subcarrier oscillator, chroma subcarrier oscillator, quadrature chroma modulators, and RF oscillators and modulators for two low VHF channels.- MOS/LSl Databook, National Semiconductor, Santa Clara, CA, 1977, p 4-48-4-49. (View)

View full Circuit Diagram | Comments | Reading(3557)

PARALLEL_TELEPHONE_CONNECTION

Published:2009/7/7 21:42:00 Author:May

When the handset is lifted and power is applied to the circuit, Q2 is fed base current through R2, which in tum drives Q1. C2 is charged via R3 in series with D1 to (VZ1 - 0.7) V. When the minimum operating VDD voltage is reached, power on reset occurs via the rc network of C1 and R8. Q2 is maintained in the on condition by G1, while Q3, and hence Q4, are held off by G2. The DF320 network appears in parallel with the telephone as an impedance more than 10 KΩ in the standby condition with the telephone network connected in circuit through Q1. On recognition of the first keyed digit, the DF320 clock is started. M1 then goes to logic 1 causing Q2 and Q1 to turn off, and Q3 and Q4 to turn on. Hence, the majority of the line loop current now flows through Q4 and Z1. When impulsing occurs, Q3 and Q4 are turned off by DP acting on G2. Line loop current is then reduced to approximately 50 μA taken through R2, R4, and G2 in series. When dialing in, complete M1 goes to logic O, causing the telephone network to be reconnected. The DF320 then returns to the static standby condition. If the line loop is interrupted by the cradle switch during dialing, impulsing will continue until C2 discharges to a voltage, such that R8 pulls CE to logic O, causing the DF320 to reset. The diode bridge protects the network from line polarity reversal. (View)

View full Circuit Diagram | Comments | Reading(1148)

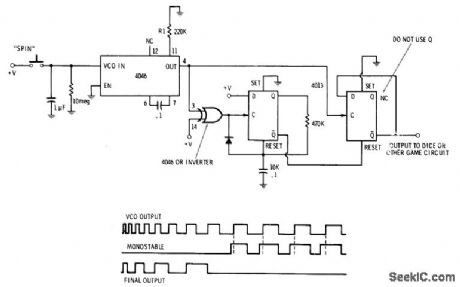

DICE_OR_ROULETTE_RUNDOWN

Published:2009/7/7 21:39:00 Author:May

4046 PLL connected as VCO is set at twice desired maximum rate for dice or roulette-wheel counters. Pressing spin button momentarily to start action charges 1-uF capacitor to sypply voltage and jumps VCO to highest frequency. Output frequency then decreases rapidly as capacitor is discharged by 10megohm resistor. Output is stopped by using retriggerable mono to drive other half of 4013 dual D flip-flop. When frequency drops below value at which monotimes out, mono resets flip-flop and holds it to stop display.-D. Lancaster, CMOS Cookbook, Howard W. Sams, Indianpolis, IN, 1977, p 252-254. (View)

View full Circuit Diagram | Comments | Reading(3114)

HOCKEY_TENNIS_HANDBALL

Published:2009/7/7 21:34:00 Author:May

Uses National have sound. MM57100 TV game chip to provide logic for generatingbackgrounds, paddles, ball, and dig ital scoring Circuit generates all necessary timing (sync, blanking, and burst) to interface with interface directly to antenna terminals of set.-MM57100 TV game chip to provide Iogic for ing (sync, blanking, and burst) to interface with circuit of standard TV receiver. With addition ofchroma, audio, and RF modulator, circuit will interface directly to antenna terminals of set.-''MOS/LSI Databook, National Semiconductor,Santa Clara, CA, 1977, p 4-37-4-47. (View)

View full Circuit Diagram | Comments | Reading(872)

SUN_TRACKER

Published:2009/7/7 21:29:00 Author:May

In solar cell array applications and solar instrumentation, it is desirable to monitor the approximate position of the sun to allow efficient automatic alignment. The L14G1 lens can provide about 15° of accuracy in a simple level sensing circuit, and a full hemisphere can be monitored with about 150 phototransistors. The sun provides = 80 mW/cm2 to the L14G1 when on the centerline. This will keep the output down to≤0.5 V for θ≤7.5°. The sky provides ≈0.5 mW/cm2 to the L14G1 and will keep the output greater than 10 V when viewed. White clouds viewed from above can lower this voltage to ≈5 V on some devices. This circuit can directly drive TTL logic by using the 5-V supply and changing the load resistor to 430 Ω. Different bright objects can also be located with the same type of circuitry simply by adjusting the resistor values to provide the desired sensitivity. (View)

View full Circuit Diagram | Comments | Reading(3812)

_LIGHT_CONTROLLED_ONE_SHOT_TINER

Published:2009/7/7 21:27:00 Author:May

This circuit uses A1 of the CA3290 BiMOS dual voltage comparator to sense a change in light diode current. A2, a one-shot timer, is triggered by the A1 output. If the light source to the photodiode is interrupted, the circuit output switches to a low state for approximately 60 s.

(View)

View full Circuit Diagram | Comments | Reading(588)

1_kHz_N_PATH_NOTCH_FILTER

Published:2009/7/7 21:24:00 Author:May

Combination of DG508 eight-channel CMOS multiplexer with low-pass and bandpass active filters provides 1-kHZ notch filter having Q of 1330 and 3-dB bandwidth of 0.75 Hz at 1 kHz. Low-pass filter introduces 180° phase shift at 1 kHz. Amplifier sums original signal in phase-shifted bandpass output from N-path filter, canceling 1-kHz components in original signal to produce desired notch characteristic.-″Analog Switches and Their Applications, SiIiconix. Santa Clara,GA,1976,p5-18-5-20. (View)

View full Circuit Diagram | Comments | Reading(2154)

SERIES_TELEPHONE_CONNECTION

Published:2009/7/7 21:21:00 Author:May

Here is a simple method of series connection into the telephone set suitable for PABX or short line applications. When the telephone handset is lifted, C1 is charged via Dl to (VZ1 - 0.7) V and DF320 power on reset occurs. When the first keyed digit is recognized, Ml goes to logic 1, muting the telephone network by switching on the low on resistance JFET Q1, and maximizing the line-loop current for impulsing. lmpulsing occurs through DP switching Q2, and hence Q3 turns off. Rapid discharge of C1 through Z1 is prevented during line break by blocking diode D1. When dialing is complete, the circuit returns to the static standby condition, and Q1 is switched off. The circuit reset, during a line interruption by the cradle switch, is for the parallel connection mode. (View)

View full Circuit Diagram | Comments | Reading(2297)

HEADS_TAILS_FLIPPER

Published:2009/7/7 21:18:00 Author:May

Uses only half of 7400 quad NAND gate as gated clock driving half of 7473 JK flip-flop. With power switch closed, LEDs representing heads and tails flash on and off at clock frequency, Closing FLIP switch stops clock randomly, leaving one LED on to give equivalent of tossing coin for heads/tails call.-G. Young,JK Flip-Flops and Clocked Logic, Kilobaud, July 1977, p 66-70 and 72-73. (View)

View full Circuit Diagram | Comments | Reading(1207)

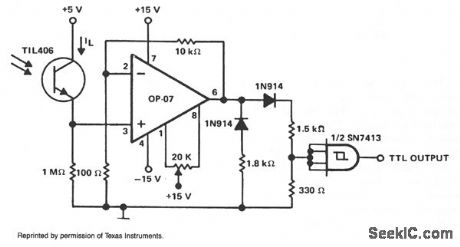

OPTICAL_SENSOR_TO_TTL_INTERFACE

Published:2009/7/7 21:17:00 Author:May

This circuit is designed to detect a low light level at the sensor, amplify the signal, and provide a TTL-level output. When the optical sensor detects low-level light, on condition, its output is small and must be amplified. An amp with very low input bias current and high input resistance must be used to detect the on condition. When sensor TlL406 is in the on condition, its output is assumed to be 250 nA (allowing a safety margin). This results in a 250-mV signal being applied to the noninverting input of amplifier OP-07.Because of the circuit configuration, the OP-07 provides a gain of 100 and its output is in positive saturation. The OP-07 output level is applied to a loading network that provides the basic TTL level. (View)

View full Circuit Diagram | Comments | Reading(2870)

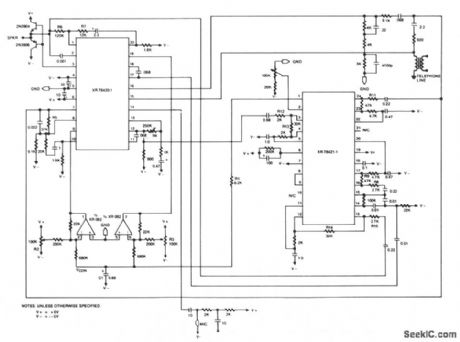

SPEAKERPHONE

Published:2009/7/7 21:17:00 Author:May

This circuit consists of two audio channels, a control circuit, and a hybrid interface circuit. The gain of each audio channel is controlled by the control circuitry, with the use of a voltage controlled amplifier (VCA). The inputs to the control circuit are obtained from each of the audio channels. The hybrid interface circuit performs three important functions. First, it couples the Tx channel signal to the telephone line. Second, it couples the signal on the telephone line to the Rx channels. And, finally, it cancels a majority of the TX signal that can couple into the Rx channel. The amount of TX signal that appears on the RX channel is called sidetone. (View)

View full Circuit Diagram | Comments | Reading(0)

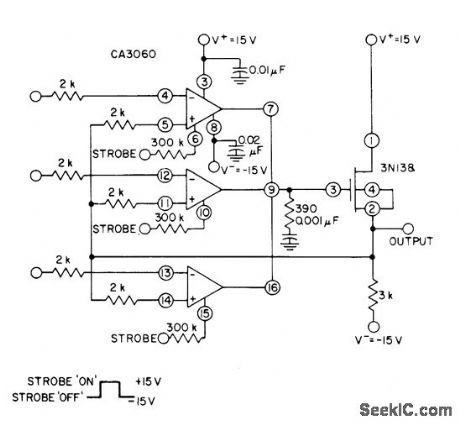

THREE_CHANNEL_FOR_DATA

Published:2009/7/7 21:15:00 Author:May

Each input channel uses CA3060 variable opamp as high-impedance voltage follower driving output MOSFET serving as buffer and power amplifier. Cascade arrangement of opamps with MOSFET provides open-loop voltage gain in excess of 100 dB.- Circuit Ideas for RCA Linear ICs, RCA Solid State Division, Somerville, NJ, 1977, p16. (View)

View full Circuit Diagram | Comments | Reading(598)

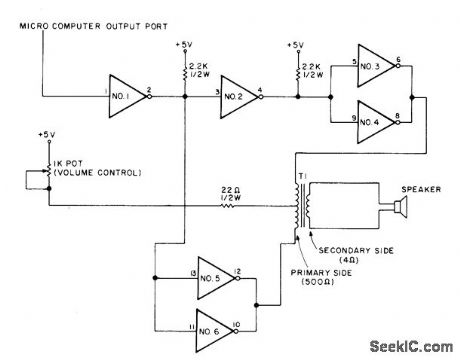

PLOP_FOR_GAMES

Published:2009/7/7 21:15:00 Author:May

Section 1 of 7406 TTL hex inverter can be attached to output port and driven by program loop, to provide sound effects for computer games. When output port goes to logic1 (greater than +2 V). action of inverter is such that paralleled inverters 3 and 4 go to 0 and draw current through primary of T1, making loudspeaker produce single plopping sound.When outputport goes to 0, another plop is produced. If output port is switched between 0 and 1 fast enough, loudspeaker output will be tone at switching frequency.-D. Parks, Adding Plop to Your System, Kilobaud, May 1977, p 98. (View)

View full Circuit Diagram | Comments | Reading(689)

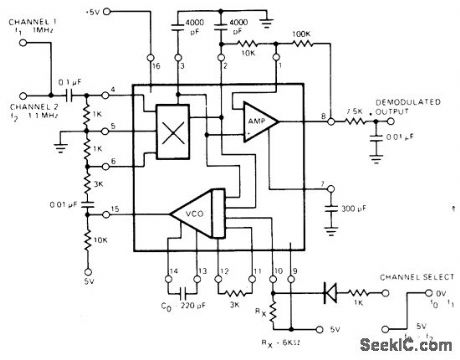

TIME_MULTIPLEXING_TWO_FM_CHANNELS

Published:2009/7/7 21:13:00 Author:May

Digital programming capability of Exar XR-215 PLL IC makes possible time-multiplexing de-modulator between two FM channels, at 1.0 and 1.1 MHz. Channel-select logic signal is applied to pin 10, and both input channels are applied simultaneously to PLL input pin 4.- Phase-Locked Loop Data Book, Exar Integrated Systems, Sunnyvale, CA, 1978, p 21-28. (View)

View full Circuit Diagram | Comments | Reading(570)

FLAME_MONITOR

Published:2009/7/7 21:13:00 Author:May

Monitoring a flame and directly switching a 120-V load is easily accomplished using the L14G1 for point sources of light. For light sources which subtend over 10°of arc, the L14C1 should be used and the illumination levels raised by a factor of 5. This circuit provides zero voltage switching to eliminate phase controlling. (View)

View full Circuit Diagram | Comments | Reading(629)

TELEPHONE_REPEATER

Published:2009/7/7 21:12:00 Author:May

View full Circuit Diagram | Comments | Reading(769)

LASER_DIODE_PULSERS

Published:2009/7/7 21:11:00 Author:May

The laser diode pulser is a simple drive circuit capable of driving the laser diode with 10-A, 20-ns pulses. For a 0.1% duty cycle, the repetition rate will be 50 kHz. A complementary emitter follower is used as a driver. Switching speed is determined by the fT of the bipolar transistors used and the impedance of the drive source. A faster drive circuit is shown. It can supply higher peak gate current to switch the IRF520 very quickly. This circuit uses a MOSPOWER totem-pole stage to drive the high power switch.The upper MOSFET is driven by a bootstrap circuit. Typical switching times for this circuit are about 10 ns for both turn-on and turn-off.

(View)

View full Circuit Diagram | Comments | Reading(2307)

| Pages:241/471 At 20241242243244245246247248249250251252253254255256257258259260Under 20 |

Circuit Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit