CD74HC648, CD74HC648E, CD74HC648EN Selling Leads, Datasheet

MFG:GS Package Cooled:DIP D/C:98

CD74HC648, CD74HC648E, CD74HC648EN Datasheet download

Part Number: CD74HC648

MFG: GS

Package Cooled: DIP

D/C: 98

MFG:GS Package Cooled:DIP D/C:98

CD74HC648, CD74HC648E, CD74HC648EN Datasheet download

MFG: GS

Package Cooled: DIP

D/C: 98

Want to post a buying lead? If you are not a member yet, please select the specific/related part number first and then fill the quantity and your contact details in the "Request for Quotation Form" on the left, and then click "Send RFQ".Your buying lead can then be posted, and the reliable suppliers will quote via our online message system or other channels soon.

TOP

PDF/DataSheet Download

Datasheet: CD74HC648

File Size: 50834 KB

Manufacturer: Intersil

Download : Click here to Download

PDF/DataSheet Download

Datasheet: CD7232CS

File Size: 342887 KB

Manufacturer:

Download : Click here to Download

PDF/DataSheet Download

Datasheet: CD7232CS

File Size: 342887 KB

Manufacturer:

Download : Click here to Download

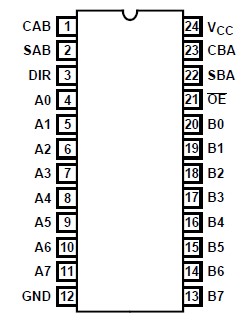

The Harris CD74HC646 and CD74HC648 are octal bus transceivers/registers with three-state non-inverting outputs. The Harris CD74HC648 is an octal bus transceiver/register with three-state inverting outputs. These devices are bus transceivers with D-type flip-flops which act as internal storage registers. Data on the A bus or the B bus can be clocked into the registers on the LOW-to-HIGH transition of either CAB or CBA clock inputs. Outputs enable (OE) and direction (DIR) inputs control the transceiver functions. Data present at the high impedance output can be stored in either register or both but only one of the two buses can be enabled as outputs at any one time. The select controls (SAB and SBA) can multiplex stored and transparent (real time) data. The direction control determines which data bus will receive data when the output enable (OE) is LOW. In the high impedance mode (output enable HIGH), A data can be stored in one register and B data can be stored in the other register. The clocks are not gated with the direction (DIR) and output enable (OE) terminals; data at the A or B terminals can be clocked into the storage flip-flops at any time.