Features: ` Code Compatible with Zilog Z80® CPU

` Extended Instructions

` Two Chain-Linked DMA Channels

` Low Power-Down Modes

` On-Chip Interrupt Controllers

` Three On-Chip Wait-State Generators

` On-Chip Oscillator/Generator

` Expanded MMU Addressing (up to 1 MB)

` Clocked Serial I/O Portn Two 16-Bit Counter/Timers

` Two Enhanced UARTs (up to 512 Kbps)

` Clock Speeds: 6, 8, 10, 20, 33 MHz

` Operating Range: 5V (3.3V@ 20 MHz)

` Operating Temperature Range: 0 to +70

`-40 to +85 Extended Temperature Range

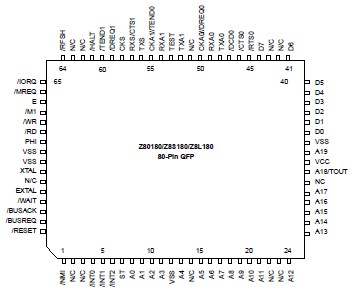

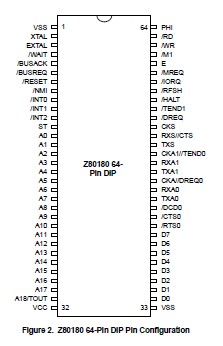

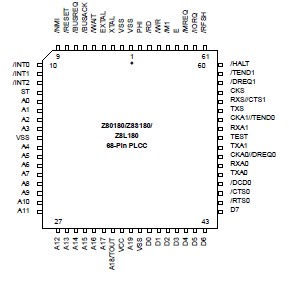

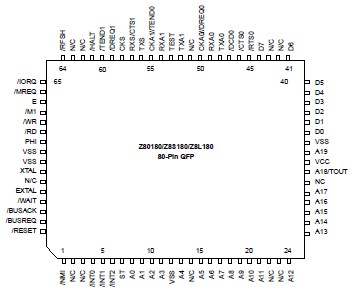

` Three Packaging Styles

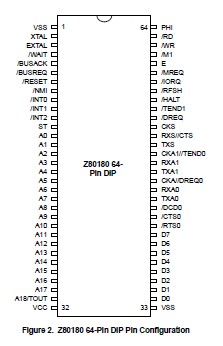

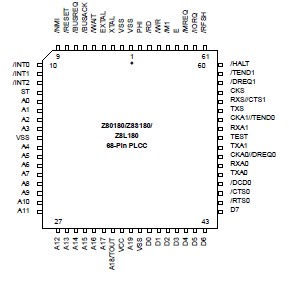

68-Pin PLCC

64-Pin DIP

80-Pin QFP

Pinout

Specifications

Specifications

| Item |

Symbol |

Value |

Unit |

| Supply Voltage |

Vcc |

-0.3 ~ +7.0 |

V |

| Input Voltage |

Vin |

-0.3 ~ Vcc +0.3 |

V |

| Operating Temperature |

Topr |

0 ~ 70 |

|

| Extended Temperature |

Text |

-40 ~ 85 |

|

| Storage Temperature |

Tstg |

-55 ~ +150 |

|

Note: Permanent LSI damage may occur if maximum ratings are exceeded. Normal operation should be under recommended operating conditions. If these conditions are exceeded, it could affect reliability of LSI.

DescriptionThe enhanced Z80180/Z8S180/Z8L180™ significantly improves on the previous Z80180 models while still providing full backward compatibility with existing Zilog Z80 devices. The Z80180/Z8S180/Z8L180 now offers faster execution speeds, power saving modes, and EMI noise reduction.

This enhanced Z180 design also incorporates additional feature enhancements to the ASCIs, DMAs, and Icc STANDBY Mode power consumption. With the addition of "ESCC-like" Baud Rate Generators (BRGs), the two ASCIs now have the flexibility and capability to transfer data asynchronously at rates of up to 512 Kbps. In addition, the ASCI receiver has added a 4-byte First In First Out (FIFO) which can be used to buffer incoming data to reduce the incidence of overrun errors. The DMAs have been modified to allow for a "chain-linking" of the two DMA channels when set to take their DMA requests from the same peripherals device. This feature allows for non-stop DMA operation between the two DMA channels, reducing the amount of CPU intervention (Figure 1).

Not only does the Z80180/Z8S180/Z8L180 consume less power during normal operations than the previous model, it has also been designed with three modes intended to further reduce the power consumption. Zilog reduced Icc power consumption during STANDBY Mode to a minimum of 10mA by stopping the external oscillators and internal clock. The SLEEP mode reduces power by placing the CPU into a "stopped" state, thereby consuming less current while the on-chip I/O device is still operating. The SYSTEM STOP mode places both the CPU and the onchip peripherals into a "stopped" mode, thereby reducing power consumption even further.

A new clock doubler feature has been implemented in the Z80180/Z8S180/Z8L180 device that allows the programmer to double the internal clock from that of the external clock. This provides a systems cost savings by allowing the use of lower cost, lower frequency crystals instead of the higher cost, and higher speed oscillators.

The Enhanced Z180 is housed in 80-pin QFP, 68-pin PLCC, and 64-pin DIP packages.

Z8L180 Data Sheet

Z8L180 Data Sheet