Features: * Fully hardware implemented, 0.8mm CMOS Technology.

* Very high speed response of A20 GATE & reset.

* Support PS2 style mouse.

* Compatible with all major BIOS, including AWARD, PHOENIX and AMI.

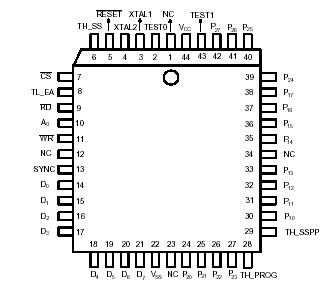

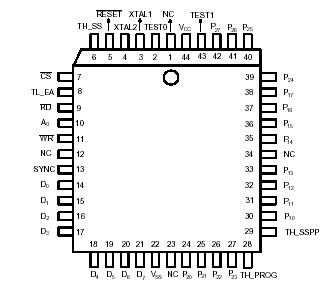

* 40 pin PDIP and 44 pin PLCC packages.Pinout Description

DescriptionThe internal timer counting is based on an 8Mhz clock input from X1, X2 ( or X2, with X1 connected to ground). After the deassertion of RESET#, the VT82C42 will drive high at pin P23 and pin P27. After 6 ms (6 x 8 clocks) of driving, the VT82C42 will check on pins T1 & P10; if both pins are low, then the VT82C42 will switch to PS/2 mode. Otherwise, the VT82C42 will remain in AT mode.

If the VT82C42 is in AT mode after the self test, then it will drive P24 and P25 low with all other ports high. If the VT82C42 is in PS/2 mode, then it will drive P24, P25, P22, and P27 low with all other ports high. The VT82C42 will not change its driving value until it receives the command "AA" from the host. When receiving the command "AA" from the host, the VT82C42 will prepare a "55" in its output buffer and drive P24 (reflecting the internal OBF flag) high within 6 clocks. This response time is the typical active time for internal IBF flag. After this initialization procedure, the VT82C42 will drive P26 low (AT mode) or drive P26 and P23 low (PS/2 mode) in order for the keyboard and mouse interface to receive data from keyboard or mouse.

When the keyboard or mouse toggles the interface (KBCLK, KBDATA, MSCLK,MSDATA), the controller receives data from the serial interface and stores the received data into its internal output buffer. If the received data is from the keyboard, a scan code translation is executed before the data is sent to the output buffer. The VT82C42 also raises P24 or P25 to indicate a output buffer full. The host is signaled to issue a read command to the data port to read the received data out. When the VT82C42 receives data in the normal mode (pin 25 on DIP40 or pin 28 on PLCC44 parts connected to VCC) and the status of P17 is low, then the controller will not raise the P24, nor activate its internal OBF flag. It looks like the controller will consume the income data itself. And if the data is from the mouse, the controller will still raise P25 to indicate that data is coming from mouse. However, if the VT82C42 is in Mouse LockTM mode (pin 25 on DIP40 or pin 28 on PLCC44 parts connected to GND), the data from either keyboard or mouse will be prohibited from sending to the host.

VT82C42 Data Sheet

VT82C42 Data Sheet